# ELECTRONC CIRCUIT ANALYSIS LECTURE NOTES (R22A0408)

B.TECH (II YEAR – II SEM) (2023-24)

#### Prepared by:

**DR. CHINNA RAO,** Associate Professor **Mr. SHIVARAJ KUMAR,** Assistant Professor

**Department of Electronics and Communication Engineering**

# MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY

(Autonomous Institution – UGC, Govt. of India)

Recognized under 2(f) and 12 (B) of UGC ACT 1956

(Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC – 'A' Grade - ISO 9001:2015 Certified)

Maisammaguda, Dhulapally (Post Via. Kompally), Secunderabad – 500100, Telangana State, India

#### MALLA REDDY COLLEGE OF ENGINEERING AND TECHNOLOGY

II Year B. Tech. ECE- II Sem

*L/T/P/C* 3/-/-/3

#### (R22A0408) ELECTRONIC CIRCUIT ANALYSIS

#### Course Objectives:

Upon completing this course, the student twill be able to

- 1. Learn the concepts of Power Amplifiers.

- 2. To give understanding of tuned amplifier circuits

- 3. Understand various multivibrators using transistors and sweep circuits.

#### UNIT - I

**Large Signal Amplifiers:** Class A Power Amplifier- Series fed and Transformer coupled, Conversion Efficiency, Class B Power Amplifier- Push Pull and Complimentary Symmetry configurations, Conversion Efficiency, Principle of operation of Class AB and Class —C and D Amplifiers.

#### UNIT-II

**Tuned Amplifiers:** Introduction, single Tuned Amplifiers – Q-factor, frequency response, Double Tuned Amplifiers – Q-factor, frequency response, Concept of stagger tuning and synchronous tuning

#### UNIT - III

**Multivibrators**: Analysis and Design of Bistable, Monostable, Astable Multivibrators and Schmitt trigger using Transistors.

#### **UNIT-IV**

**Time Base Generators:** General features of a Time base Signal, Methods of Generating Time Base Waveform, concepts of Transistor Miller and Bootstrap Time Base Generator, Methods of Linearity improvement.

#### UNIT - V

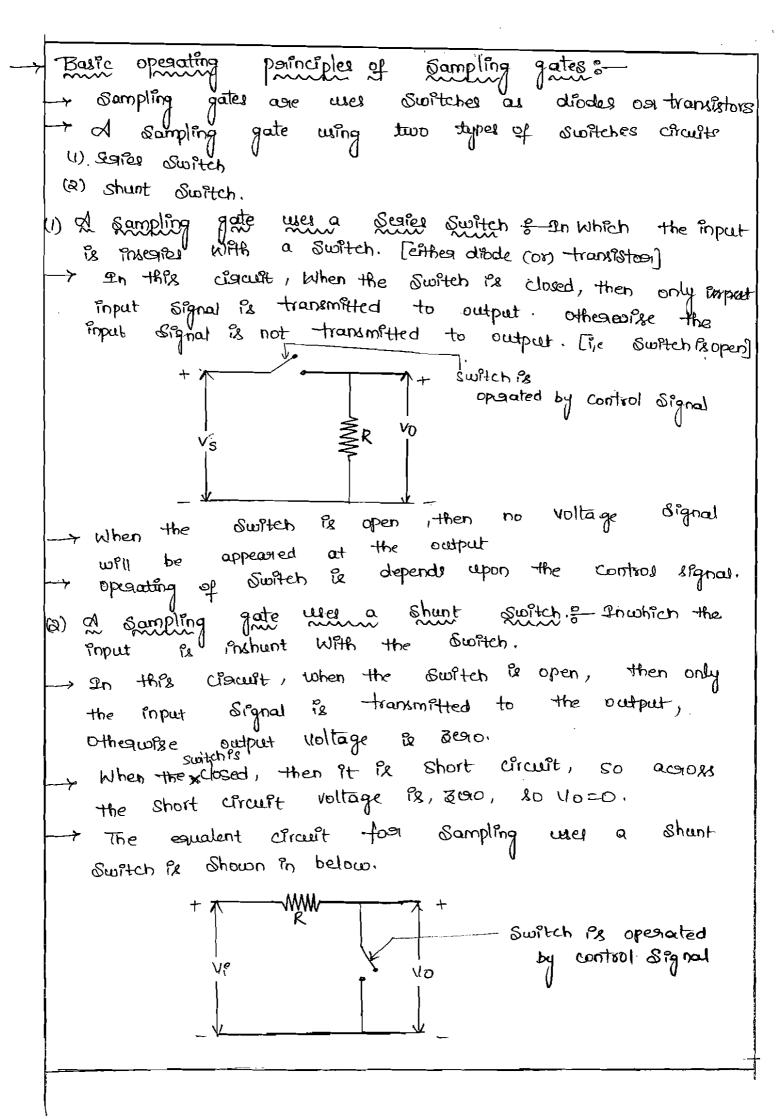

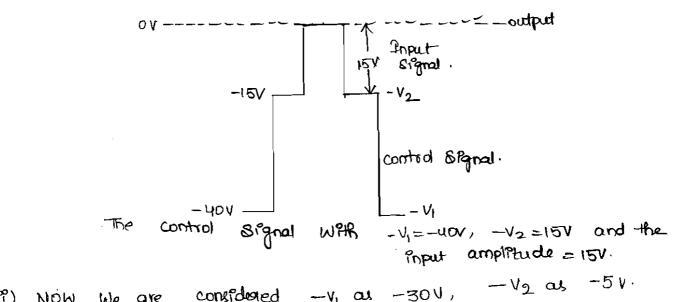

**Sampling Gates:** Basic operating principles of Sampling Gates, Unidirectional and Bidirectional Sampling Gates, Four Diode Sampling Gate, Reduction of pedestal in Gate Circuits

**Synchronization and Frequency Division:** Pulse Synchronization of Relaxation Devices, Frequency division in Sweep Circuits, Stability of Relaxation Devices,

#### **TEXT BOOKS:**

- 1. Jacob Millman, Christos C Halkias Integrated Electronics, , McGraw Hill Education.

- 2. J. Millman, H. Taub and Mothiki S. PrakashRao Pulse, Digital and Switching Waveforms –2<sup>nd</sup> Ed., TMH, 2008,

#### REFERENCE BOOKS:

- 1. David A. Bell Electronic Devices and Circuits, 5<sup>th</sup> Ed., Oxford.

- 2. Robert L. Boylestead, Louis Nashelsky Electronic Devices and Circuits theory, 11<sup>th</sup> Ed.,Pearson, 2009

- 3. Ronald J. Tocci Fundamentals of Pulse and Digital Circuits, 3<sup>rd</sup> Ed., 2008.

- 4. David A. Bell Pulse, Switching and Digital Circuits, 5<sup>th</sup> Ed., Oxford, 2015.

#### Course Outcomes:

Upon completing this course, the student will be able to

- 1. Design the power amplifiers

- 2. Design the tuned amplifiers and analyse is frequency response

- 3. Design Multivibrators and sweep circuits for various applications.

- 4. Utilize the concepts of synchronization, frequency division and sampling gates

### UNIT-I LARGE SIGNAL AMPLIFIERS

In practice, any amplifier consists of few stages of amplification. If we consider audio amplification, it has several stages of amplification, depending upon our requirement.

#### **Power Amplifier**

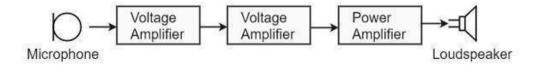

After the audio signal is converted into electrical signal, it has several voltage amplifications done, after which the power amplification of the amplified signal is done just before the loud speaker stage. This is clearly shown in the below figure.

While the voltage amplifier raises the voltage level of the signal, the power amplifier raises the power level of the signal. Besides raising the power level, it can also be said that a power amplifier is a device which converts DC power to AC power and whose action is controlled by the input signal.

The DC power is distributed according to the relation, DC

power input = AC power output + losses

#### **Power Transistor**

For such Power amplification, a normal transistor would not do. A transistor that is manufactured to suit the purpose of power amplification is called as a **Power transistor**.

A Power transistor differs from the other transistors, in the following factors.

- It is larger in size, in order to handle large powers.

- The collector region of the transistor is made large and a heat sink is placed at the collector-base junction in order to minimize heat generated.

- The emitter and base regions of a power transistor are heavily doped.

- Due to the low input resistance, it requires low input power.

Hence there is a lot of difference in voltage amplification and power amplification. So, let us now try to get into the details to understand the differences between a voltage amplifier and a power amplifier.

#### **Difference between Voltage and Power Amplifiers:**

Let us try to differentiate between voltage and power amplifier.

#### **Voltage Amplifier**

The function of a voltage amplifier is to raise the voltage level of the signal. A voltage

amplifier is designed to achieve maximum voltage amplification.

The voltage gain of an amplifier is given by

$Av=\theta(Rc/Rin)$

The characteristics of a voltage amplifier are as follows -

- The base of the transistor should be thin and hence the value of  $\beta$  should be greater than 100.

- The resistance of the input resistor  $R_{in}$  should be low when compared to collector load  $R_{C}$ .

- The collector load R<sub>C</sub> should be relatively high. To permit high collector load, the voltage amplifiers are always operated at low collector current.

- The voltage amplifiers are used for small signal voltages.

#### **Power Amplifier**

The function of a power amplifier is to raise the power level of input signal. It is required to deliver a large amount of power and has to handle large current.

The characteristics of a power amplifier are as follows –

- The base of transistor is made thicken to handle large currents. The value of  $\beta$  being ( $\beta$  > 100) high.

- The size of the transistor is made larger, in order to dissipate more heat, which is produced during transistor operation.

- Transformer coupling is used for impedance matching.

- Collector resistance is made low.

The comparison between voltage and power amplifiers is given below in a tabular form.

| S.No | Particular        | Voltage Amplifier    | Power Amplifier                 |

|------|-------------------|----------------------|---------------------------------|

| 1    | β                 | High (>100)          | Low (5 to 20)                   |

| 2    | R <sub>C</sub>    | High (4-10 KΩ)       | Low (5 to 20 Ω)                 |

| 3    | Coupling          | Usually R-C coupling | Invariably transformer coupling |

| 4    | Input voltage     | Low (a few m V)      | High (2-4 V)                    |

| 5    | Collector current | Low (≈ 1 mA)         | High (> 100 mA)                 |

| 6    | Power output      | Low                  | High                            |

| 7    | Output impendence | High (≈ 12 K Ω)      | Low (200 Ω                      |

The Power amplifiers amplify the power level of the signal. This amplification is done in the last stage in audio applications. The applications related to radio frequencies employ radio power amplifiers. But the **operating point** of a transistor plays a very important role in determining the efficiency of the amplifier. The **main classification** is done based on this mode of operation.

The classification is done based on their frequencies and also based on their mode of operation.

#### **Classification Based on Frequencies**

Power amplifiers are divided into two categories, based on the frequencies they handle. They are as follows.

- Audio Power Amplifiers The audio power amplifiers raise the power level of signals that have audio frequency range (20 Hz to 20 KHz). They are also known as Small signal power amplifiers.

- Radio Power Amplifiers Radio Power Amplifiers or tuned power amplifiers raise

the power level of signals that have radio frequency range (3 KHz to 300 GHz). They

are also known as large signal power amplifiers.

#### **Classification Based on Mode of Operation**

On the basis of the mode of operation, i.e., the portion of the input cycle during which collector current flows, the power amplifiers may be classified as follows.

- Class A Power amplifier When the collector current flows at all times during the full cycle of signal, the power amplifier is known as class A poweramplifier.

- Class B Power amplifier When the collector current flows only during the positive half cycle of the input signal, the power amplifier is known as class B power amplifier.

- Class C Power amplifier When the collector current flows for less than half cycle of the input signal, the power amplifier is known as class C power amplifier.

There forms another amplifier called Class AB amplifier, if we combine the class A and class B amplifiers so as to utilize the advantages of both. Before going into the details of these amplifiers, let us have a look at the important terms that have to be considered to determine the efficiency of an amplifier.

#### **Terms Considering Performance**

The primary objective of a power amplifier is to obtain maximum output power. In order to

achieve this, the important factors to be considered are collector efficiency, power dissipation capability and distortion. Let us go through them in detail.

#### **Collector Efficiency**

This explains how well an amplifier converts DC power to AC power. When the DC supply is given by the battery but no AC signal input is given, the collector output at such a condition is observed as **collector efficiency**.

The collector efficiency is defined as

$\eta$ =average a.c power output / average d.c power input to transistor

The main aim of a power amplifier is to obtain maximum collector efficiency. Hence the higher the value of collector efficiency, the efficient the amplifier will be.

#### **Power Dissipation Capacity**

Every transistor gets heated up during its operation. As a power transistor handles large currents, it gets more heated up. This heat increases the temperature of the transistor, which alters the operating point of the transistor. So, in order to maintain the operating point stability, the temperature of the transistor has to be kept in permissible limits. For this, the heat produced has to be dissipated. Such a capacity is called as Power dissipation capability.

**Power dissipation capability** can be defined as the ability of a power transistor to dissipate the heat developed in it. Metal cases called heat sinks are used in order to dissipate the heat produced in power transistors.

#### Distortion

A transistor is a non-linear device. When compared with the input, there occur few variations in the output. In voltage amplifiers, this problem is not pre-dominant as small currents are used. But in power amplifiers, as large currents are in use, the problem of distortion certainly arises.

**Distortion** is defined as the change of output wave shape from the input wave shape of the amplifier. An amplifier that has lesser distortion produces a better output and hence considered efficient.

We have already come across the details of transistor biasing, which is very important for the operation of a transistor as an amplifier. Hence to achieve faithful amplification, the biasing of the transistor has to be done such that the amplifier operates over the linear region.

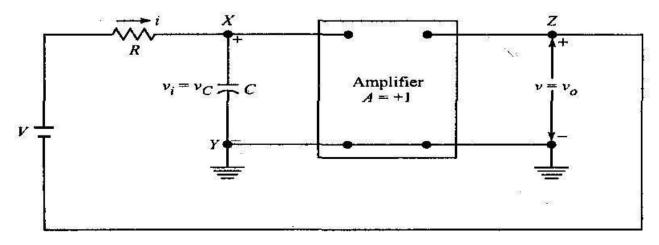

A Class A power amplifier is one in which the output current flows for the entire cycle of the AC input supply. Hence the complete signal present at the input is amplified at the output. The following figure shows the circuit diagram for Class A Power amplifier.

From the above figure, it can be observed that the transformer is present at the collector as a load. The use of transformer permits the impedance matching, resulting in the transference of maximum power to the load e.g. loud speaker.

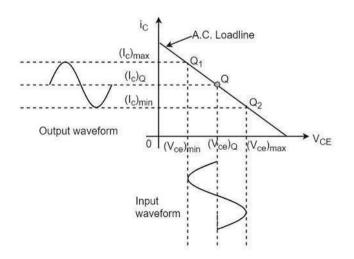

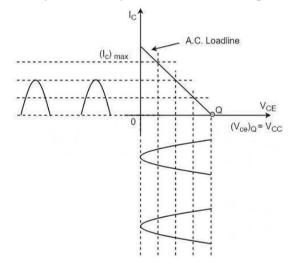

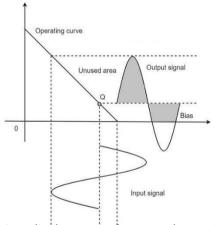

The operating point of this amplifier is present in the linear region. It is so selected that the current flows for the entire ac input cycle. The below figure explains the selection of operating point.

The output characteristics with operating point Q is shown in the figure above. Here  $(I_c)_Q$  and  $(V_{ce})_Q$  represent no signal collector current and voltage between collector and emitter respectively. When signal is applied, the Q-point shifts to  $Q_1$  and  $Q_2$ . The output current increases to  $(I_c)_{max}$  and decreases to  $(I_c)_{min}$ . Similarly, the collector-emitter voltage increases to  $(V_{ce})_{max}$  and decreases to  $(V_{ce})_{min}$ .

D.C. Power drawn from collector battery V<sub>cc</sub> is given by

$$Pin=voltage \times current = V_{CC}(I_C)_O$$

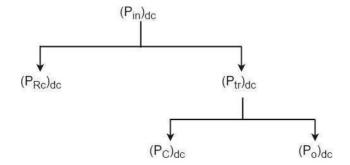

This power is used in the following two parts -

Power dissipated in the collector load as heat is given by

$$P_{RC}$$

=(current)<sup>2</sup>×resistance=(IC)<sup>2</sup> $_{Q}R_{C}$

• Power given to transistor is given by

$$P_{tr}=P_{in}-P_{RC}=V_{CC}-(I_C)_{2Q}R_C$$

When signal is applied, the power given to transistor is used in the following two parts -

A.C. Power developed across load resistors RC which constitutes the a.c. power output.

$$(P_O)ac=I^2R_C=V^2/R_C=(V_m/\sqrt{2})/R_C=V^2m/2R_C$$

- Where I is the R.M.S. value of a.c. output current through load, V is the R.M.S. value of a.c. voltage, and V<sub>m</sub> is the maximum value of V.

- The D.C. power dissipated by the transistor (collector region) in the form of heat, i.e.,  $(P_C)_{dc}$

We have represented the whole power flow in the following diagram.

This class A power amplifier can amplify small signals with least distortion and the output will be an exact replica of the input with increased strength.

#### Let us now try to draw some expressions to represent efficiencies.

#### Overall Efficiency

The overall efficiency of the amplifier circuit is given by

$$(\eta)_{overall} = rac{a.\ c\ power\ delivered\ to\ the\ load}{total\ power\ delivered\ by\ d.\ c\ supply}$$

$$= rac{(P_O)_{ac}}{(P_{in})_{de}}$$

#### Collector Efficiency

The collector efficiency of the transistor is defined as

$$(\eta)_{collector} = rac{average \ a. \ c \ power \ output}{average \ d. \ c \ power \ input \ to \ transistor} \ = rac{(P_O)_{ac}}{(P_{tr})_{dc}}$$

Expression for overall efficiency

$$\begin{split} (P_O)_{ac} &= V_{rms} \times I_{rms} \\ &= \frac{1}{\sqrt{2}} \left[ \frac{(V_{ce})_{max} - (V_{ce})_{min}}{2} \right] \times \frac{1}{\sqrt{2}} \left[ \frac{(I_C)_{max} - (I_C)_{min}}{2} \right] \\ &= \frac{[(V_{ce})_{max} - (V_{ce})_{min}] \times [(I_C)_{max} - (I_C)_{min}]}{8} \end{split}$$

#### **Advantages of Class A Amplifiers**

The advantages of Class A power amplifier are as follows -

- The current flows for complete input cycle

- It can amplify small signals

- The output is same as input

- No distortion is present

#### **Disadvantages of Class A Amplifiers**

The advantages of Class A power amplifier are as follows –

- Low power output

- Low collector efficiency

The class A power amplifier as discussed in the previous chapter, is the circuit in which the output current flows for the entire cycle of the AC input supply. We also have learnt about the

disadvantages it has such as low output power and efficiency. In order to minimize those effects, the transformer coupled class A power amplifier has been introduced.

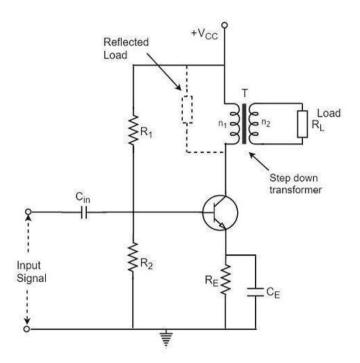

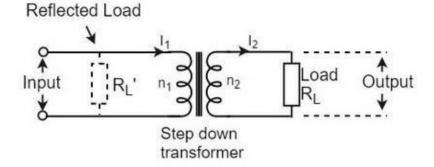

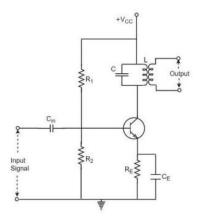

The **construction of class A power amplifier** can be understood with the help of below figure. This is similar to the normal amplifier circuit but connected with a transformer in the collector load.

Here  $R_1$  and  $R_2$  provide potential divider arrangement. The resistor Re provides stabilization,  $C_e$  is the bypass capacitor and  $R_e$  to prevent a.c. voltage. The transformer used here is a step-down transformer. The high impedance primary of the transformer is connected to the high impedance collector circuit. The low impedance secondary is connected to the load (generally loud speaker).

#### **Transformer Action:**

The transformer used in the collector circuit is for impedance matching.  $R_L$  is the load connected in the secondary of a transformer.  $R_L'$  is the reflected load in the primary of the transformer.

The number of turns in the primary are  $n_1$  and the secondary are  $n_2$ . Let  $V_1$  and  $V_2$  be the primary and secondary voltages and  $I_1$  and  $I_2$  be the primary and secondary currents respectively. The below figure shows the transformer clearly.

We know that

$$\frac{V_1}{V_2} = \frac{n_1}{n_2} \ and \ \frac{I_1}{I_2} = \frac{n_1}{n_2}$$

Or

$$V_1 = \frac{n_1}{n_2} V_2 \ and I_1 = \frac{n_1}{n_2} I_2$$

Hence

$$rac{V_1}{I_1} = \left(rac{n_1}{n_2}

ight)^2 rac{V_2}{I_2}$$

But  $V_1/I_1 = R_L' = effective input resistance$

And  $V_2/I_2 = R_L = effective$  output resistance

Therefore,

$$R_L' = \left(\frac{n_1}{n_2}\right)^2 R_L = n^2 R_L$$

Where

$$n = \frac{number\ of\ turns\ in\ primary}{number\ of\ turns\ in\ secondary} = \frac{n_1}{n_2}$$

A power amplifier may be matched by taking proper turn ratio in step down transformer.

#### **Circuit Operation**

If the peak value of the collector current due to signal is equal to zero signal collector current, then the maximum a.c. power output is obtained. So, in order to achieve complete amplification, the operating point should lie at the center of the load line.

The operating point obviously varies when the signal is applied. The collector voltage varies in opposite phase to the collector current. The variation of collector voltage appears across the primary of the transformer.

#### **Circuit Analysis**

The power loss in the primary is assumed to be negligible, as its resistance is very small.

The input power under dc condition will be

$$(P_{in})_{dc} = (P_{tr})_{dc} = V_{CC} \times (I_C)_O$$

Under maximum capacity of class A amplifier, voltage swings from  $(V_{\text{Ce}})_{\text{max}}$  to zero and current from  $(I_{\text{c}})_{\text{max}}$  to zero.

Hence

$$\begin{split} V_{rms} &= \frac{1}{\sqrt{2}} \left[ \frac{(V_{ce})_{max} - (V_{ce})_{min}}{2} \right] = \frac{1}{\sqrt{2}} \left[ \frac{(V_{ce})_{max}}{2} \right] = \frac{2V_{CC}}{2\sqrt{2}} \\ &= \frac{V_{CC}}{\sqrt{2}} \end{split}$$

$$\begin{split} I_{rms} &= \frac{1}{\sqrt{2}} \left[ \frac{(I_C)_{max} - (I_C)_{min}}{2} \right] = \frac{1}{\sqrt{2}} \left[ \frac{(I_C)_{max}}{2} \right] = \frac{2(I_C)_Q}{2\sqrt{2}} \\ &= \frac{(I_C)_Q}{\sqrt{2}} \end{split}$$

Therefore,

$$(P_O)_{ac} = V_{rms} \times I_{rms} = \frac{V_{CC}}{\sqrt{2}} \times \frac{(I_C)_Q}{\sqrt{2}} = \frac{V_{CC} \times (I_C)_Q}{2}$$

Therefore,

Collector Efficiency =

$$\frac{(P_O)_{ac}}{(P_{tr})_{dc}}$$

Or,

$$\begin{split} (\eta)_{collector} &= \frac{V_{CC} \times (I_C)_Q}{2 \times V_{CC} \times (I_C)_Q} = \frac{1}{2} \\ &= \frac{1}{2} \times 100 = 50\% \end{split}$$

The efficiency of a class A power amplifier is nearly than 30% whereas it has got improved to 50% by using the transformer coupled class A power amplifier.

#### **Advantages**

The advantages of transformer coupled class A power amplifier are as follows.

- No loss of signal power in the base or collector resistors.

- Excellent impedance matching is achieved.

- · Gain is high.

- DC isolation is provided.

#### Disadvantages

The disadvantages of transformer coupled class A power amplifier are as follows.

• Low frequency signals are less amplified comparatively.

- Hum noise is introduced by transformers.

- · Transformers are bulky and costly.

- Poor frequency response.

#### **Applications**

The applications of transformer coupled class A power amplifier are as follows.

- This circuit is where impedance matching is the main criterion.

- These are used as driver amplifiers and sometimes as output amplifiers.

- When the collector current flows only during the positive half cycle of the input signal, the power amplifier is known as **class B power amplifier**.

#### **Class B Operation**

The biasing of the transistor in class B operation is in such a way that at zero signal condition, there will be no collector current. The **operating point** is selected to be at collector cut off voltage. So, when the signal is applied, **only the positive half cycle** is amplified at the output.

The figure below shows the input and output waveforms during class B operation.

When the signal is applied, the circuit is forward biased for the positive half cycle of the input and hence the collector current flows. But during the negative half cycle of the input, the circuit is reverse biased and the collector current will be absent. Hence **only the positive half cycle** is amplified at the output.

As the negative half cycle is completely absent, the signal distortion will be high. Also, when the applied signal increases, the power dissipation will be more. But when compared to class A power amplifier, the output efficiency is increased. Well, in order to minimize the disadvantages and achieve low distortion, high efficiency and high output power, the push-pull configuration is used in this class B amplifier.

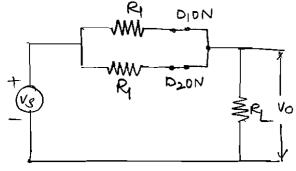

#### Class B Push-Pull Amplifier

Though the efficiency of class B power amplifier is higher than class A, as only one half cycle of the input is used, the distortion is high. Also, the input power is not completely utilized. In order to compensate these problems, the push-pull configuration is introduced in class B amplifier.

#### Construction:

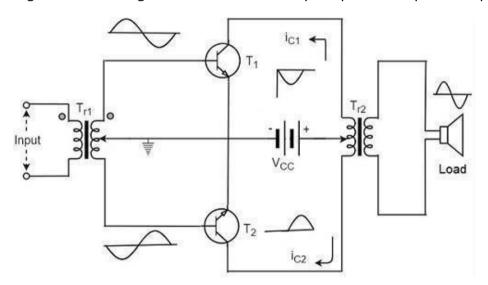

The circuit of a push-pull class B power amplifier consists of two identical transistors  $T_1$  and  $T_2$  whose bases are connected to the secondary of the center-tapped input transformer  $T_{r1}$ . The emitters are shorted and the collectors are given the  $V_{CC}$  supply through the primary of the output transformer  $T_{r2}$ .

The circuit arrangement of class B push-pull amplifier, is same as that of class A push-pull amplifier except that the transistors are biased at cut off, instead of using the biasing resistors. The figure below gives the detailing of the construction of a push-pull class B power amplifier.

The circuit operation of class B push pull amplifier is detailed below.

#### Operation

The circuit of class B push-pull amplifier shown in the above figure clears that both the transformers are center-tapped. When no signal is applied at the input, the transistors  $T_1$  and  $T_2$  are in cut off condition and hence no collector currents flow. As no current is drawn from  $V_{CC}$ , no power is wasted.

When input signal is given, it is applied to the input transformer  $T_{r1}$  which splits the signal into two signals that are  $180^{\circ}$  out of phase with each other. These two signals are given to the two identical transistors  $T_1$  and  $T_2$ . For the positive half cycle, the base of the transistor  $T_1$  becomes positive and collector current flows. At the same time, the transistor  $T_2$  has negative half cycle, which throws the transistor  $T_2$  into cutoff condition and hence no collector current flows. The waveform is produced as shown in the following figure.

For the next half cycle, the transistor  $T_1$  gets into cut off condition and the transistor  $T_2$  gets into conduction, to contribute the output. Hence for both the cycles, each transistor conducts alternately. The output transformer  $T_{r3}$  serves to join the two currents producing an almost undistorted output waveform.

#### **Power Efficiency of Class B Push-Pull Amplifier**

The current in each transistor is the average value of half sine loop. For half sine loop,  $I_{dc}$  is given by  $I_{dc} = \frac{(I_C)_{max}}{\pi}$

Therefore,

$$(p_{in})_{dc} = 2 imes \left[ rac{(I_C)_{max}}{\pi} imes V_{CC}

ight]$$

Here factor 2 is introduced as there are two transistors in push-pull amplifier.

R.M.S. value of collector current =  $(I_C)_{max}/\sqrt{2}$

R.M.S. value of output voltage =  $V_{CC}/\sqrt{2}$

Under ideal conditions of maximum power

Therefore,

$$(P_O)_{ac} = rac{(I_C)_{max}}{\sqrt{2}} imes rac{V_{CC}}{\sqrt{2}} = rac{(I_C)_{max} imes V_{CC}}{2}$$

Now overall maximum efficiency

$$egin{aligned} \eta_{overall} &= rac{(P_O)_{ac}}{(P_{in})_{dc}} \ &= rac{(I_C)_{max} imes V_{CC}}{2} imes rac{\pi}{2(I_C)_{max} imes V_{CC}} \ &= rac{\pi}{4} = 0.785 = 78.5\% \end{aligned}$$

The collector efficiency would be the same.

Hence the class B push-pull amplifier improves the efficiency than the class A push-pull amplifier.

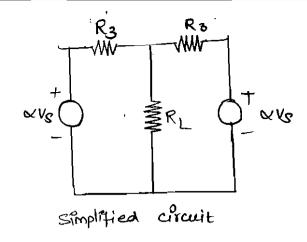

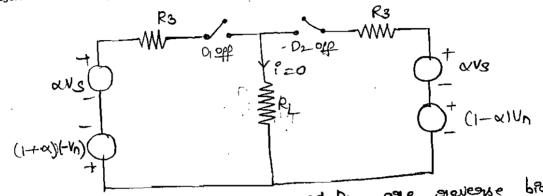

#### Complementary Symmetry Push-Pull Class B Amplifier

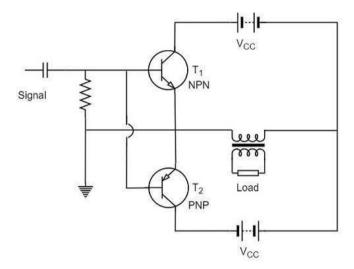

The push pull amplifier which was just discussed improves efficiency but the usage of center-tapped transformers makes the circuit bulky, heavy and costly. To make the circuit simple and to improve the efficiency, the transistors used can be complemented, as shown in the following circuit diagram.

The above circuit employs a NPN transistor and a PNP transistor connected in push pull configuration. When the input signal is applied, during the positive half cycle of the input signal, the NPN transistor conducts and the PNP transistor cuts off. During the negative half cycle, the NPN transistor cuts off and the PNP transistor conducts.

In this way, the NPN transistor amplifies during positive half cycle of the input, while PNP transistor amplifies during negative half cycle of the input. As the transistors are both complement to each other, yet act symmetrically while being connected in push pull configuration of class B, this circuit is termed as **Complementary symmetry push pull class B amplifier**.

#### **Advantages**

The advantages of Complementary symmetry push pull class B amplifier are as follows.

- As there is no need of center tapped transformers, the weight and cost are reduced.

- Equal and opposite input signal voltages are not required.

#### **Disadvantages**

The disadvantages of Complementary symmetry push pull class B amplifier are as follows.

- It is difficult to get a pair of transistors (NPN and PNP) that have similar characteristics.

- We require both positive and negative supply voltages.

The class A and class B amplifier so far discussed has got few limitations. Let us now try to combine these two to get a new circuit which would have all the advantages of both class A and class B amplifier without their inefficiencies. Before that, let us also go through another important problem, called as **Cross over distortion**, the output of class B encounters with.

#### **Cross-over Distortion:**

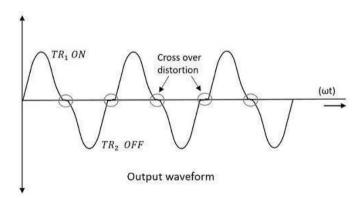

In the push-pull configuration, the two identical transistors get into conduction, one after the other and the output produced will be the combination of both.

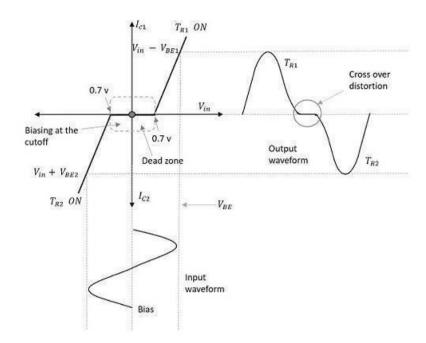

When the signal changes or crosses over from one transistor to the other at the zero voltage point, it produces an amount of distortion to the output wave shape. For a transistor in order to conduct, the base emitter junction should cross 0.7v, the cut off voltage. The time taken for a transistor to get ON from OFF or to get OFF from ON state is called the **transition period**.

At the zero voltage point, the transition period of switching over the transistors from one to the other, has its effect which leads to the instances where both the transistors are OFF at a time. Such instances can be called as **Flat spot** or **Dead band** on the output wave shape.

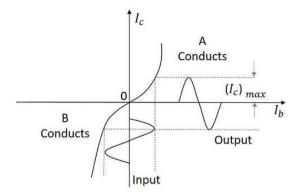

The above figure clearly shows the cross over distortion which is prominent in the output waveform. This is the main disadvantage. This cross over distortion effect also reduces the overall peak to peak value of the output waveform which in turn reduces the maximum power output. This can be more clearly understood through the non-linear characteristic of the waveform as shown below.

It is understood that this cross-over distortion is less pronounced for large input signals, where as it causes severe disturbance for small input signals. This cross over distortion can be eliminated if the conduction of the amplifier is more than one half cycle, so that both the transistors won't be OFF at the same time.

This idea leads to the invention of class AB amplifier, which is the combination of both class A and class B amplifiers, as discussed below.

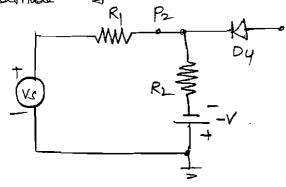

#### **Class AB Power Amplifier**

As the name implies, class AB is a combination of class A and class B type of amplifiers. As class A has the problem of low efficiency and class B has distortion problem, this class AB is emerged to eliminate these two problems, by utilizing the advantages of both the classes.

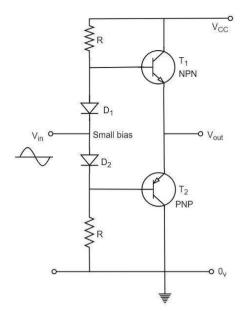

The cross over distortion is the problem that occurs when both the transistors are OFF at the same instant, during the transition period. In order to eliminate this, the condition has to be chosen for more than one half cycle. Hence, the other transistor gets into conduction, before the operating transistor switches to cut off state. This is achieved only by using class AB configuration, as shown in the following circuit diagram.

Therefore, in class AB amplifier design, each of the push-pull transistors is conducting for slightly more than the half cycle of conduction in class B, but much less than the full cycle of conduction of class A.

The conduction angle of class AB amplifier is somewhere between 180° to 360° depending upon the operating point selected. This is understood with the help of below figure.

The small bias voltage given using diodes  $D_1$  and  $D_2$ , as shown in the above figure, helps the operating point to be above the cutoff point. Hence the output waveform of class AB results as seen in the above figure. The crossover distortion created by class B is overcome by this class AB, as well the inefficiencies of class A and B don't affect the circuit.

So, the class AB is a good compromise between class A and class B in terms of efficiency and linearity having the efficiency reaching about 50% to 60%. The class A, B and AB amplifiers are called as **linear amplifiers** because the output signal amplitude and phase are linearly related to the input signal amplitude and phase.

#### **Class C Power Amplifier**

When the collector current flows for less than half cycle of the input signal, the power amplifier is known as **class C power amplifier**. The efficiency of class C amplifier is high while linearity is poor. The conduction angle for class C is less than 180°. It is generally around 90°, which means the transistor remains idle for more than half of the input signal. So, the output current will be delivered for less time compared to the application of input signal.

The following figure shows the operating point and output of a class C amplifier.

This kind of biasing gives a much improved efficiency of around 80% to the amplifier, but introduces heavy distortion in the output signal. Using the class C amplifier, the pulses produced at its output can be converted to complete sine wave of a particular frequency by using LC circuits in its collector circuit.

The types of amplifiers that we have discussed so far cannot work effectively at radio frequencies, even though they are good at audio frequencies. Also, the gain of these amplifiers is such that it will not vary according to the frequency of the signal, over a wide range. This allows the amplification of the signal equally well over a range of frequencies and does not permit the selection of particular desired frequency while rejecting the other frequencies.

# UNIT-II TUNED AMPLIFIERS

Tuned amplifiers are the amplifiers that are employed for the purpose of **tuning**. Tuning means selecting. Among a set of frequencies available, if there occurs a need to select a particular frequency, while rejecting all other frequencies, such a process is called **Selection**. This selection is done by using a circuit called as **Tuned circuit**.

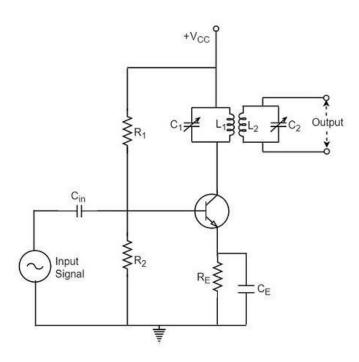

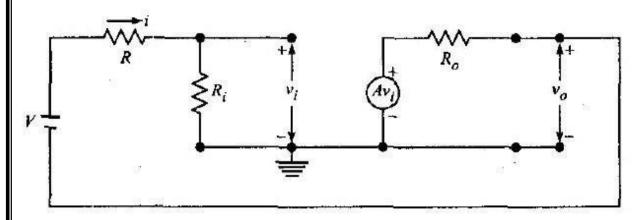

When an amplifier circuit has its load replaced by a tuned circuit, such an amplifier can be called as a **Tuned amplifier circuit**. The basic tuned amplifier circuit looks as shown below.

The tuner circuit is nothing but a LC circuit which is also called as **resonant** or **tank circuit**. It selects the frequency. A tuned circuit is capable of amplifying a signal over a narrow band of frequencies that are centered at resonant frequency.

When the reactance of the inductor balances the reactance of the capacitor, in the tuned circuit at some frequency, such a frequency can be called as **resonant frequency**. It is denoted by  $\mathbf{f}_r$ .

The formula for resonance is

#### **Types of Tuned Circuits**

A tuned circuit can be Series tuned circuit (Series resonant circuit) or Parallel tuned circuit (parallel resonant circuit) according to the type of its connection to the main circuit.

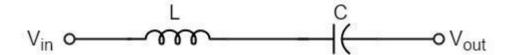

#### **Series Tuned Circuit**

The inductor and capacitor connected in series make a series tuned circuit, as shown in the following circuit diagram.

At resonant frequency, a series resonant circuit offers low impedance which allows high current through it. A series resonant circuit offers increasingly high impedance to the frequencies far from the resonant frequency.

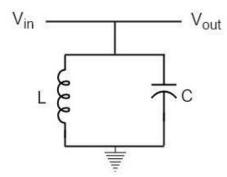

#### **Parallel Tuned Circuit**

The inductor and capacitor connected in parallel make a parallel tuned circuit, as shown in the below figure.

At resonant frequency, a parallel resonant circuit offers high impedance which does not allow high current through it. A parallel resonant circuit offers increasingly low impedance to the frequencies far from the resonant frequency.

#### **Characteristics of a Parallel Tuned Circuit**

The frequency at which parallel resonance occurs (i.e. reactive component of circuit current becomes zero) is called the resonant frequency  $\mathbf{f_r}$ . The main characteristics of a tuned circuit are as follows.

#### **Impedance**

The ratio of supply voltage to the line current is the impedance of the tuned circuit. Impedance offered by LC circuit is given by

Supply voltage / Lineequation=V / I

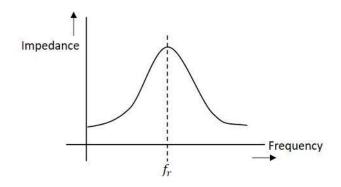

At resonance, the line current increases while the impedance decreases. The below figure represents the impedance curve of a parallel resonance circuit.

Impedance of the circuit decreases for the values above and below the resonant frequency  $\mathbf{f}_{r}$ . Hence the selection of a particular frequency and rejection of other frequencies is possible.

To obtain an equation for the circuit impedance, let us consider Line Current *I=ILcos*

$V/Zr=V/Z_1\times R/Z_1$

$1/Zr=R/Z^2L$

1/Zr = CR/L

Since,  $Z_{2L}=L/C$

Therefore, circuit impedance Z<sub>r</sub> is obtained as

$Z_R=L/CR$

Thus at parallel resonance, the circuit impedance is equal to L/CR.

#### **Circuit Current**

At parallel resonance, the circuit or line current I is given by the applied voltage divided by the circuit impedance  $Z_r$  i.e.,

Line Current *I=VZr*

Where *Zr=L/CR*

Because Z<sub>r</sub> is very high, the line current I will be very small.

#### **Quality Factor**

For a parallel resonance circuit, the sharpness of the resonance curve determines the selectivity. The smaller the resistance of the coil, the sharper the resonant curve will be. Hence the inductive reactance and resistance of the coil determine the quality of the tuned circuit.

The ratio of inductive reactance of the coil at resonance to its resistance is known as **Quality factor**. It is denoted by **Q**.

$Q=X_L/R=2\pi frLR$

The higher the value of Q, the sharper the resonance curve and the better the selectivity will be.

#### **Advantages of Tuned Amplifiers**

The following are the advantages of tuned amplifiers.

- The usage of reactive components like L and C, minimizes the power loss, which makes the tuned amplifiers efficient.

- The selectivity and amplification of desired frequency is high, by providing higher impedance at resonant frequency.

- A smaller collector supply VCC would do, because of its little resistance in parallel tuned circuit.

It is important to remember that these advantages are not applicable when there is a high resistive collector load.

#### **Frequency Response of Tuned Amplifier**

For an amplifier to be efficient, its gain should be high. This voltage gain depends upon  $\beta$ , input impedance and collector load. The collector load in a tuned amplifier is a tuned circuit.

The voltage gain of such an amplifier is given by

Voltage gain =  $Bz_c/Z_{in}$

Where  $Z_C$  = effective collector load and  $Z_{in}$  = input impedance of the amplifier.

The value of  $Z_C$  depends upon the frequency of the tuned amplifier. As  $Z_C$  is maximum at resonant frequency, the gain of the amplifier is maximum at this resonant frequency.

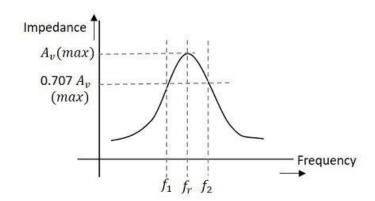

#### Bandwidth

The range of frequencies at which the voltage gain of the tuned amplifier falls to 70.7% of the maximum gain is called its **Bandwidth**. The range of frequencies between  $f_1$  and  $f_2$  is called as bandwidth of the tuned amplifier. The bandwidth of a tuned amplifier depends upon the Q of the LC circuit i.e., upon the sharpness of the frequency response. The value of Q and the bandwidth are inversely proportional.

The figure below details the bandwidth and frequency response of the tuned amplifier.

#### Relation between Q and Bandwidth

The quality factor Q of the bandwidth is defined as the ratio of resonant frequency to bandwidth, i.e.,

Q=fr / BW

In general, a practical circuit has its Q value greater than 10. Under this condition, the resonant frequency at parallel resonance is given by  $fr=1/\sqrt{2\pi LC}$

There are two main types of tuned amplifiers. They are -

- Single tuned amplifier

- Double tuned amplifier

#### **Single Tuned Amplifier**

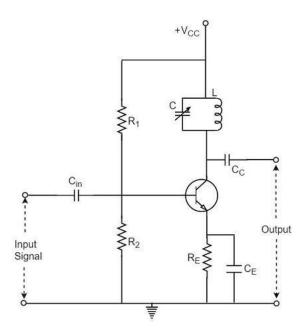

An amplifier circuit with a single tuner section being at the collector of the amplifier circuit is called as Single tuner amplifier circuit.

#### Construction

A simple transistor amplifier circuit consisting of a parallel tuned circuit in its collector load, makes a single tuned amplifier circuit. The values of capacitance and inductance of the tuned circuit are selected such that its resonant frequency is equal to the frequency to be amplified.

The following circuit diagram shows a single tuned amplifier circuit.

The output can be obtained from the coupling capacitor  $C_{\mathbb{C}}$  as shown above or from a secondary winding placed at L.

#### **Operation**

The high frequency signal that has to be amplified is applied at the input of the amplifier. The resonant frequency of the parallel tuned circuit is made equal to the frequency of the signal applied by altering the capacitance value of the capacitor C, in the tuned circuit. At this stage, the tuned circuit offers high impedance to the signal frequency, which helps to offer high output across the tuned circuit. As high impedance is offered only for the tuned frequency, all the other frequencies which get lower impedance are rejected

by the tuned circuit. Hence the tuned amplifier selects and amplifies the desired frequency signal.

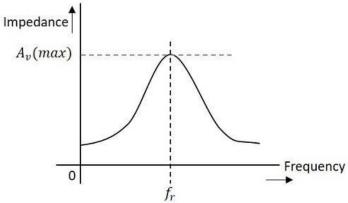

#### **Frequency Response**

The parallel resonance occurs at resonant frequency  $f_r$  when the circuit has a high Q. the resonant frequency  $f_r$  is given by

$fr=1/\sqrt{2\pi LC}$

The following graph shows the frequency response of a single tuned amplifier circuit.

At resonant frequency  $f_r$  the impedance of parallel tuned circuit is very high and is purely resistive. The voltage across  $R_L$  is therefore maximum, when the circuit is tuned to resonant frequency. Hence the voltage gain is maximum at resonant frequency and drops off above and below it. The higher the Q, the narrower will the curve be.

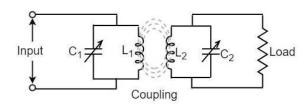

#### **Double Tuned Amplifier**

An amplifier circuit with a double tuner section being at the collector of the amplifier circuit is called as Double tuner amplifier circuit.

#### Construction

The construction of double tuned amplifier is understood by having a look at the following figure. This circuit consists of two tuned circuits  $L_1C_1$  and  $L_2C_2$  in the collector section of the amplifier. The signal at the output of the tuned circuit  $L_1C_1$  is coupled to the other tuned circuit  $L_2C_2$  through mutual coupling method. The remaining circuit details are same as in the single tuned amplifier circuit, as shown in the following circuit diagram.

#### Operation

The high frequency signal which has to be amplified is given to the input of the amplifier. The tuning circuit  $L_1C_1$  is tuned to the input signal frequency. At this condition, the tuned circuit offers high reactance to the signal frequency. Consequently, large output appears at the output of the tuned circuit  $L_1C_1$  which is then coupled to the other tuned circuit  $L_2C_2$  through mutual induction. These double tuned circuits are extensively used for coupling various circuits of radio and television receivers.

#### **Frequency Response of Double Tuned Amplifier**

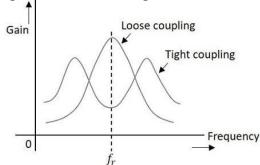

The double tuned amplifier has the special feature of **coupling** which is important in determining the frequency response of the amplifier. The amount of mutual inductance between the two tuned circuits states the degree of coupling, which determines the frequency response of the circuit.

In order to have an idea on the mutual inductance property, let us go through the basic principle.

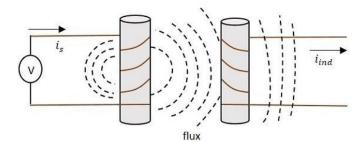

#### **Mutual Inductance**

As the current carrying coil produces some magnetic field around it, if another coil is brought near this coil, such that it is in the magnetic flux region of the primary, then the varying magnetic flux induces an EMF in the second coil. If this first coil is called as **Primary coil**, the second one can be called as a **Secondary coil**. When the EMF is induced in the secondary coil due to the varying magnetic field of the primary coil, then such phenomenon is called as the

•

#### Mutual Inductance.

The figure below gives an idea about this.

The current  $i_s$  in the figure indicate the source current while  $i_{ind}$  indicates the induced current. The flux represents the magnetic flux created around the coil. This spreads to the secondary coil also. With the application of voltage, the current  $i_s$  flows and flux gets created. When the current is varies the flux gets varied, producing  $i_{ind}$  in the secondary coil, due to the Mutual inductance property.

#### Coupling

Under the concept of mutual inductance coupling will be as shown in the figure below.

When the coils are spaced apart, the flux linkages of primary coil  $L_1$  will not link the secondary coil  $L_2$ . At this condition, the coils are said to have **Loose coupling**. The resistance reflected from the secondary coil at this condition is small and the resonance curve will be sharp and the circuit Q is high as shown in the figure below.

## UNIT III MULTIVIBRATORS

A transistor can be used as a switch. It has three regions of operation. When both Emitter-to-base and collector-base junctions are reverse biased, the transistor operates in the cut-off region and it acts as an open switch. When the emitter base junction is forward biased and the Collector base junction is reverse biased, it operates in the active region and acts as auf amplifier. When both the emitter-base and collector-base junctions are forward biased, it Operates in the saturation region and acts as a closed switch. When the transistor is switched! from cut-off to saturation and from saturation to cut-off with negligible active region, the transistor is operated as a switch. When the transistor is in saturation, junction voltages are'i very small but the operating currents are large. When the transistor is in cut-off, the currents\* are zero (except small leakage current) but the junction voltages are large.

In Below Figure the transistor Q can be used to connect and disconnect the load *RL* from the source Vcc When Q is saturated it is like a closed switch from collector to emitter and when Q is cutoff it is like an open switch from collector to emitter.

Referring to the output characteristics shown in Figure (b), the region below the IB = 0 curve is the cut-off region. The intersection of the load line with IB = 0 curve is the cut-off point. At this point, the base current is zero and the collector current is negligible. The emitter diode comes out of forward bias and the normal transistor action is lost, i.e, VCE(cut-off) = Vcc. The transistor appears like an open switch.

The intersection of the load line with the IB = IB(sat) curve is called the saturation point. At this point, the base current is IB(sat) and the collector current is maximum. 'At saturation, the collector diode comes out of cut-off and again the normal transistor action is lost, i.e. Ic(sat) = Vcc / RL. IB(sat) represents the minimum base current required to bring the transistor into saturation. For 0 < IB < IB(sat), the transistor operates in the active region. If the base current is greater than IB(sat), the collector current approximately equals Vcc / RL and the transistor appears like a closed switch.

#### TRANSISTOR SWITCHING TIMES

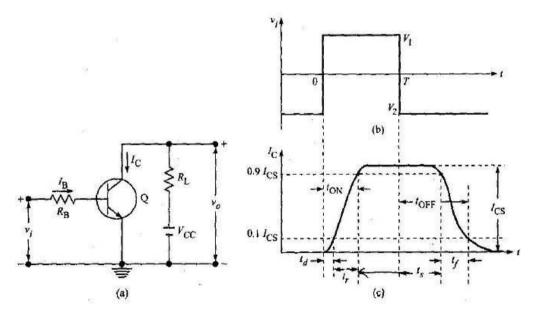

When the transistor acts as a switch, it is either in cut-off or in saturation. To consider the behaviour of the transistor as it makes transition from one state to the other, consider the circuit shown in below figure (a) driven by the pulse waveform shown in Figure (b). The pulse waveform makes transitions between the voltage levels V2 and V1. At V2 the transistor is at cutoff and at V the transistor is in saturation. The input waveform v; is applied between the base and the emitter through a resistor RB.

Figure a) Transistor as a Switch b) input waveform c) the response of collector current versus time

The response of the collector current ic to the input waveform, together with its time relationship to the waveform is shown in Figure (c), The collector current does not immediately respond to the input signal. Instead there is a delay, and the time that elapses during this delay, together with the time required for the current to rise to 10% of its maximum (saturation) value (Ics = Vcc / RL)) is called the delay time td. The current waveform has a nonzero rise time tr, which

is the rise time required for the current to rise from 10% to 90% of Ics- The total turn-on time TON is the sum of the *delay time* and the rise time, i.e. TON = td + tr.

When the input signal returns to its initial state, the collector current again fails to respond immediately. The interval which elapses between the transition of the input waveform and the time when Ic has dropped to 90% of Ics is called the *storage time ts*. The storage interval is followed by the fall time Iy, which is the time required for 7C to fall from 90% to 10% of Ics- The turn-off time tOFF is defined as the sum of the storage and fall times, i.e. TOFF = tr + tf We shall now consider the physical reasons for the existence of each of these times.

#### The delay time

There are three factors that contribute to the delay time. First there is a delay which results from the fact that, when the driving signal is applied to the transistor input, a non-zero time is required to charge up the junction capacitance so that the transistor may be brought, from cut-off to the active region. Second, even when the transistor has been brought to the point where minority carriers have begun to cross the emitter junction into the base, a nonzero time is required before these carriers can cross the base region to the collector junction and be recorded as collector current. Finally, a nonzero time is required before the collector current can rise to 10% of its maximum value. Rise time and fall time. The rise time and fall time are due to the fact that, if a base current step is used to saturate the transistor or to return it from saturation into cutoff, the collector current must traverse the active region. The collector current increases or decreases along an exponential curve. Storage time The failure of the transistor to respond to the trailing edge of the driving pulse for the time interval *ts*, results from the fact that a transistor in saturation has a saturation charge of excess minority carriers stored in the base. The transistor cannot respond until the saturation excess charge has been removed.

#### **MULTIVIBRATORS**

Multi means many; vibrator means oscillator. A circuit which can oscillate at a number of frequencies is called a multivibrator. Basically there are three types of multivibrators:

- 1. Bistable multivibrator

- Monostable multivibrator

- 3. Astable multivibrator

Each of these multivibrators has two states. As the names indicate, a bistable multivibrator has got two stable states, a monostable multivibrator has got only one stable state (the other state being quasi stable) and the astable multivibrator has got no stable state (both the

states being quasi stable). The stable state of a multivibrator is the state in which the device can stay permanently. Only when a proper external triggering signal is applied, it will change its state. Quasi stable state means temporarily stable state. The device cannot stay permanently in this state. After a predetermined time, the device will automatically come out of the quasi stable state.

Multivibrators find applications in a variety of systems where square waves or timed intervals are required. For example, before the advent of low-cost integrated circuits, chains of multivibrators found use as frequency dividers. A free-running multivibrator with a frequency of one-half to one-tenth of the reference frequency would accurately lock to the reference frequency. This technique was used in early electronic organs, to keep notes of different octaves accurately in tune. Other applications included early television systems, where the various line and frame frequencies were kept synchronized by pulses included in the video signal.

#### **BISTABLE MULTIVIBRATOR**

A bistable multivibrator is a multivibrator which can exist indefinitely in either of its two stable states and which can be induced to make an abrupt transition from one state to the other by means of external excitation. In a bistable multivibrator both the coupling elements are resistors (dc coupling). The bistable multivibrator is also called a multi, Eccles-Jordan circuit (after its inventors), trigger circuit, scale-of-two toggle circuit, flip-flop, and binary. There are two types of bistable multivibrators:

- 1. Collector coupled bistable multivibrator

- 2. Emitter coupled bistable multivibrator

There are two types of collector-coupled bistable multivibrators:

- 1. Fixed-bias bistable multivibrator

- 2. Self-bias bistable multivibrator

#### A FIXED-BIAS BISTABLE MULTIVIBRATOR

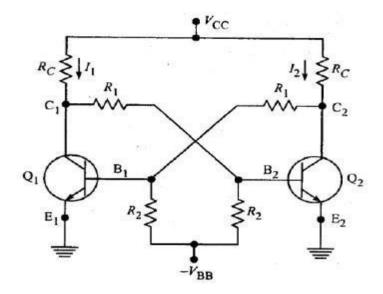

The Figure below shows the circuit diagram of a fixed-bias bistable multivibrator using transistors (inverters). Note, that the output of each amplifier is direct coupled to the input of the other amplifier.

In one of the stable states, transistor Q[ is ON (i.e. in saturation) and Q2 is OFF (i.e. in cutoff), and in the other stable state Qi is OFF and Q2 is ON. Even though the circuit is symmetrical, it is not possible for the circuit to remain in a stable state with both the transistors conducting (i.e. both operating in the active region) simultaneously and carrying equal currents. The reason is that if we assume that both the transistors are biased equally and are carrying equal currents /[ and 72 and suppose there is a minute fluctuation in the current  $1/\sim$ —let us say it increases by a small amount—then the voltage at the collector of Qi decreases. This will result in a decrease in voltage at the base of Q2. So Q2 conducts less and /2 decreases and hence the potential at the collector of Q2 increases. This results in an increase in the base potential of Qi. So, Qi conducts still more and /[ is further increased and the potential at the collector of Qt is further reduced, and so on. So, the current /\ keeps on increasing and the current /2 keeps on decreasing till Q( goes into saturation and Q2 goes into cut-off. This action takes place because of the regenerative feedback incorporated into the circuit and will occur only if the loop gain is greater than one. A stable state of a binary is one in which the voltages and currents satisfy the Kirchhoff's laws and are consistent with the device characteristics and in which, in addition, the condition of the loop gain being less than unity is satisfied.

The condition with respect to loop gain will certainly be satisfied, if either of the two devices is below cut-off or if either device is in saturation. But normally the circuit is designed such that in a stable state one transistor is in saturation and the other one is ir cut-off, because if one transistor is biased to be in cut-off and the other one to be in active region, as the temperature changes or the devices age and the device parameters vary, the quiescent point changes and the quiescent output voltage may also change appreciably Sometimes the drift may

be so much that the device operating in the active region may gc into cut-off, and with both the devices in cut-off the circuit will be useless.

#### Selection of components in the fixed-bias bistable multivibrator

In the fixed-bias binary shown in Figure 4.1., nearly the full supply voltage Vcc will appear across the transistor that is OFF. Since this supply voltage Vcc is to be reasonably smaller than the collector breakdown voltage SVce. Vcc restricted to a maximum of a few tens of volts. Under saturation conditions the collector current Ic is maximum. Hence RC must be chosen so that this value of C (= VCC/ $^{\circ}$ G) does not exceed the maximum permissible limit. The values of R1, R2 and VBB must be selected such that in one stat>le state the base current is large enough to drive the transistor into saturation whereas in the second stable state the emitter junction must be below cut-off. The signal at a collector called the output swing Vw is the change in collector voltage resulting from a transistor going from one state to the other, i.e. Vw = VCi - IC2- If the loading caused by RI can be neglected, then the collector voltage of the OFF transistor is Vcc. Since the collector saturation voltage is few tenths of a volt, then the swing Vw = Vcc, independently of RQ- VCC Component values, the supply voltages and the values of VCBO, VCBC and VCE(sat) are sufficient for the analysis of transistor binary circuits.

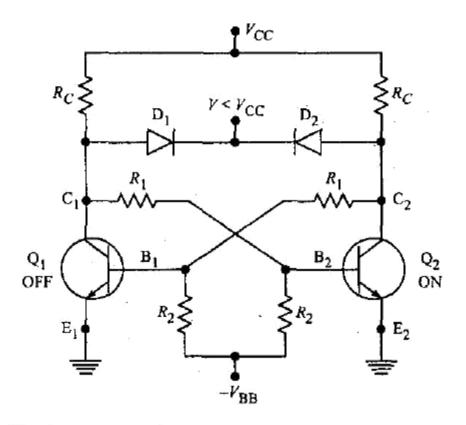

#### Loading

The bistable multivibrator may be used to drive other circuits and hence at one or both the collectors there are shunting loads, which are not shown in Figure 4.1. These loads reduce the magnitude of the collector voltage VC1 of the OFF transistor. This will result in reduction of the output voltage swing. A reduced VC[ will decrease VB2 and it is possible that Q2 may not be driven into saturation- Hence the flip-flop circuit components must be chosen such that under the heaviest load, which the binary drives, one- transistor remains in saturation while the other is in cut-off. Since the resistor RI also loads the OFF transistor, to reduce loading, the value of RI should be as large as possible compared to the value of RI. But to ensure a loop gain in excess of unity during the transition between the states, RI should be selected such that For some applications, the loading varies with the operation being performed. In such cases, the extent to which a transistor is driven into saturation is variable. A constant output swing VI = VI , arid a constant base saturation current III can be obtained by clamping the collectors to an auxiliary voltage VI < VI < VCC through the diodes III and III and III and III in Figure 4.2. As III Conducts and clamps the output to III.

#### Standard specifications

In the cut-off region, i.e. for the OFF state

$V_{\text{BE}}$  (cut-off) :  $\leq 0$  V for silicon transistor  $\leq -0.1$  V for germanium transistor

In the saturation region, i.e. for the ON state

$V_{\rm BE}$  (sat): 0.7 V for silicon transistor

0.3 V for germanium transistor

$V_{\rm CE}$  (sat) : 0.3 V for silicon transistor

0.1 V for germanium transistor

The above values hold good for n-p-n transistors. For p-n-p transistors the above values with opposite sign are to be taken.

#### Test for saturation

To test whether a transistor is really in saturation or not evaluate the collector current  $i_C$  and the base current  $i_B$  independently.

If  $i_B > i_B$  (min), where  $i_B$  (min) =  $i_C/h_{FE}$  (min) the transistor is really in saturation. If  $i_B \le i_B$  (min), the transistor is not in saturation.

#### Test for cut-off

To test whether a transistor is really cut-off or not, find its base-to-emitter voltage. If  $V_{\rm BE}$  is negative for an n-p-n transistor or positive for a p-n-p transistor, the transistor is really cut-off.

## MONOSTABLE MULTIVIBRATOR

**Monostable Multivibrators** have only **one** stable state (hence their name: "Mono"), and produce a single output pulse when it is triggered externally. Monostable multivibrators only return back to their first original and stable state after a period of time determined by the time constant of the RC coupled circuit.

Monostable multivibrators or "One-Shot Multivibrators" as they are also called, are used to generate a single output pulse of a specified width, either "HIGH" or "LOW" when a suitable external trigger signal or pulse T is applied. This trigger signal initiates a timing cycle which causes the output of the monostable to change its state at the start of the timing cycle and will remain in this second state, which is determined by the time constant of the timing capacitor, CT and the resistor, RT until it resets or returns itself back to its original (stable) state. It will then remain in this original stable state indefinitely until another input pulse or trigger signal is received. Then, Monostable Multivibrators have only ONE stable state and go through a full cycle in response to a single triggering input pulse.

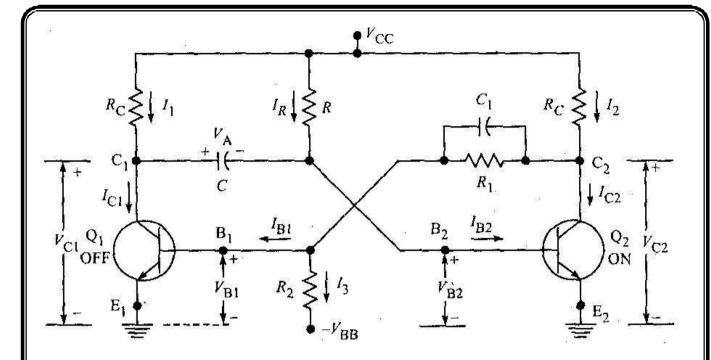

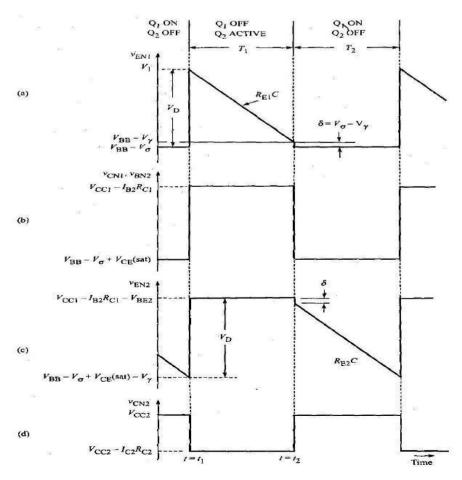

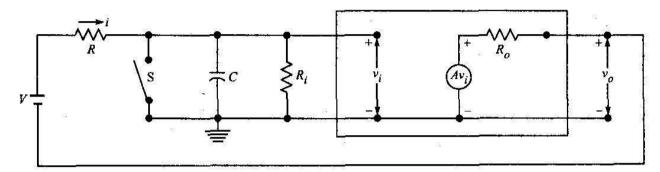

#### THE COLLECTOR COUPLED MONOSTABLE MULTIVIBRATOR

The below Figure shows the circuit diagram of a collector-to-base coupled (simply called collectorcoupled) monostable multivibrator using n-p-n transistors. The collector of Q2 is coupled to the base of Qi by a resistor R} (dc coupling) and the collector of Qt is coupled to the base of Q2 by a capacitor C (ac coupling). Ci is the commutating capacitor introduced to increase the speed of operation. The base of Qi is connected to -VBB through a resistor R2, to ensure that Q! is cut off under quiescent conditions. The base of Q2 is connected to VCc through R to ensure that Q2 is ON under quiescent conditions. In fact, R may be returned to even a small positive voltage but connecting it to Vcc is advantageous. The circuit parameters are selected such that under quiescent conditions, the monostable multivibrator finds itself in its permanent stable state with Q2ON (i.e. in saturation) and Q! OFF (i.e. in cut-off)- The multivibrator may be induced to make a transition out of its stable state by the application of a negative trigger at the base of Q2 or at the collector of Q|. Since the triggering signal is applied to only one device and not to both the devices simultaneously, unsymmetrical triggering is employed. When a negative signal is applied at the base of Q2 at  $t \sim 0$ , due to regenerative action Q2 goes to OFF state and Qi goes to ON state. When Q, is ON, a current /i flows through its Rc and hence its collector voltage drops suddenly by I\RC This drop will be instantaneously

transmitted through the coupling capacitor C to the base of Q2. So at t = 0+, the base voltage of Q2 is

$$V_{\rm BE}(\rm sat) - I_1 R_{\rm C}$$

The circuit cannot remain in this state for a long time (it stays in this state only for a finite time *T*) because when Qt conducts, the coupling capacitor *C* charges from Vcc through the conducting transistor Qi and hence the potential at the base of Q2 rises exponentially with a time constant

$(R+R_o)C \approx RC$ , where RO is the conducting transistor output impedance including the resistance Rc. When it passes the cut-in voltage Vy of Q2 (at a time t=T), a regenerative action takes place turning Q| OFF and eventually returning the multivibrator to its initial stable state. The transition from the stable state to the quasi-stable state takes place at t=0, and the reverse transition from the quasi-stable state to the stable state takes place at t=T. The time T for which the circuit is in its quasi-stable state is also referred to as the delay time, and also as the gate width, pulse width, or pulse duration. The delay time may be varied by varying the time constant t(=RC).

# Expression for the gate width T of a monostable multivibrator neglecting the reverse saturation current /CBO

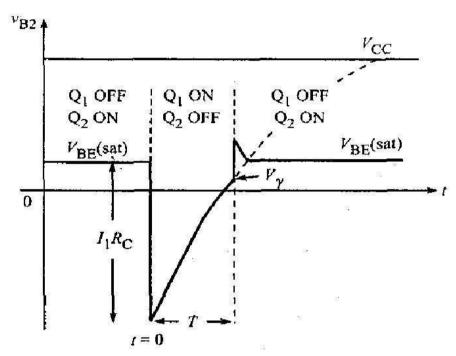

The below Figure (a) shows the waveform at the base of transistor Q2 of the monostable multivibrator

For t < 0, Q2 is ON and so vB2 = VBE(sat). At t = 0, a negative signal applied brings Q2 to OFF state and Q[ into saturation. A current I flows through Rc of Qt and hence vci drops abruptly by I c volts and so vB2 also drops by  $I \setminus RC$  instantaneously. So at t - 0, vB2 = VBE(sat) -  $I \setminus RC$ . For t > 0, the capacitor charges with a time constant RC, and hence the base voltage of Q2 rises exponentially towards VCc with the same time constant. At t = T, when this base voltage rises to the cut-in voltage level Vy of the transistor, Q2 goes to ON state, and Qj to OFF state and the pulse ends. In the interval 0 < t < 7", the base voltage of Q2, i.e. vB2 is given by

$$v_{\rm B2} = V_{\rm CC} - (V_{\rm CC} - \{V_{\rm BE}({\rm sat}) - I_1 R_{\rm C}\})e^{-t/\tau}$$

Fig a) Voltage variation at the base of Q2 during the quasi-stable state

But

$$I_1R_C = V_{CC} - V_{CE}(\text{sat})$$

(because at  $t = 0^-$ ,  $v_{C1} = V_{CC}$  and at  $t = 0^+$ ,  $v_{C1} = V_{CE}(\text{sat})$ )

$$v_{B2} = V_{CC} - [V_{CC} - \{V_{BE}(\text{sat}) - (V_{CC} - V_{CE}(\text{sat}))\}]e^{-t/\tau}$$

$$= V_{CC} - [2V_{CC} - \{V_{BE}(\text{sat}) + V_{CE}(\text{sat})\}]e^{-t/\tau}$$

At

$$t = T, v_{B2} = V_{\gamma}$$

$$\therefore V_{\gamma} = V_{CC} - [2V_{CC} - \{V_{CE}(\text{sat}) + V_{BE}(\text{sat})\}]e^{-T/\tau}$$

i.e.

$$e^{T/\tau} = \frac{2V_{CC} - [V_{CE}(\text{sat}) + V_{BE}(\text{sat})]}{V_{CC} - V_{\gamma}}$$

$$\therefore \frac{T}{\tau} = \frac{\ln \left[ 2 \left( V_{CC} - \frac{V_{CE}(\text{sat}) + V_{BE}(\text{sat})}{2} \right) \right]}{V_{CC} - V_{\gamma}}$$

i.e.

$$T = \tau \ln 2 + \tau \ln \frac{V_{CC} - \frac{V_{CE}(sat) + V_{BE}(sat)}{2}}{V_{CC} - V_{\gamma}}$$

Normally for a transistor, at room temperature, the cut-in voltage is the average of the saturation junction

$$V_{\gamma} = \frac{V_{\text{CE}}(\text{sat}) + V_{\text{BE}}(\text{sat})}{2}$$

voltages for either Ge or Si transistors, i.e.

Neglecting the second term in the expression for T

$$T = \tau \ln 2$$

$T = (R + R_o)C \ln 2 = 0.693(R + R_o)C$

but for a transistor in saturation Ra « R.

Gate width,

$$T = 0.693RC$$

The larger the *Vcc* is, compared to the saturation junction voltages, the more accura the result is. The gate width can be made very stable (almost independent of transistor characteristic supply voltages, and resistance values) if Q1 is driven into saturation during the quasi-stab state.

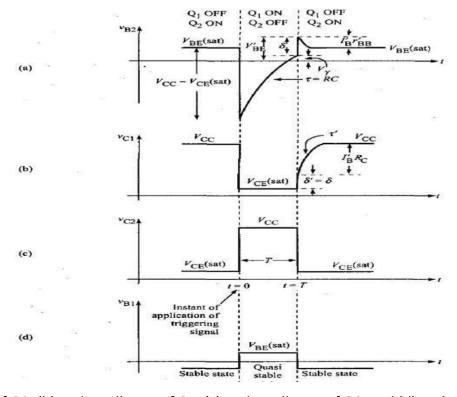

## Waveforms of the collector-coupled monostable multivibrator

The waveforms at the collectors and bases of both the transistors Q1 and Q2 are shown below

(a) at the base of Q2, (b) at the collector of Q1, (c) at the collector of Q2, and (d) at the base of Q1

## ASTABLE MULTIVIBRATOR

As the name indicates an astable multivibrator is a multivibrator with no permanent stable state. Both of its states are quasi stable only. It cannot remain in any one of its states indefinitely and keeps on oscillating between its two quasi stable states the moment it is connected to the supply. It remains in each of its two quasi stable states for only a short designed interval of time and then goes to the other quasi stable state. No triggering signal is required. Both the coupling elements are capacitors (ac coupling) and hence both the states are quasi stable. It is a free running multivibrator. It generates square waves. It is used as a master oscillator.

There are two types of astable multivibrators:

- 1. Collector-coupled astable multivibrator

- 2. Emitter-coupled astable multivibrator

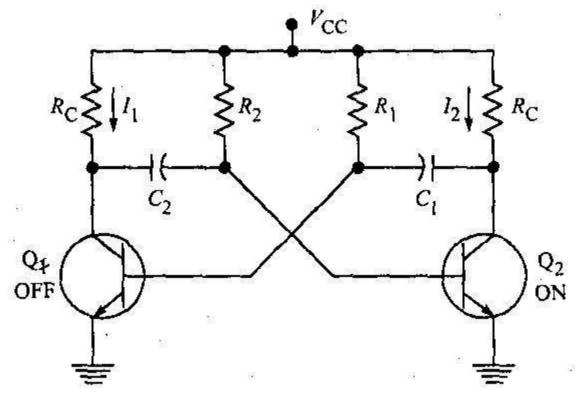

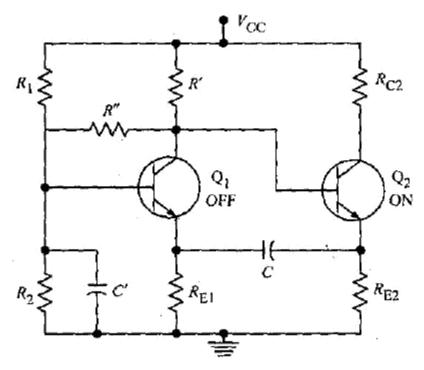

#### THE COLLECTOR-COUPLED ASTABLE MULTIVIBRATOR

The below Figure shows the circuit diagram of a collector-coupled astable multivibrator using n-p-n transistors. The collectors of both the transistors Qj and Q2 are connected to the bases

of the other transistors through the coupling capacitors Cs and C2. Since both are ac couplings, neither transistor can remain permanently at cut-off. Instead, the circuit has two quasi-stable states, and it makes periodic transitions between these states. Hence it is used as a master oscillator. No triggering signal is required for this multivibrator. The component values are selected such that, the moment it is connected to the supply, due to supply transients one

transistor will go into saturation and the other into cut-off, and also due to capacitive couplings it keeps on-oscillating between its two quasi stable states.

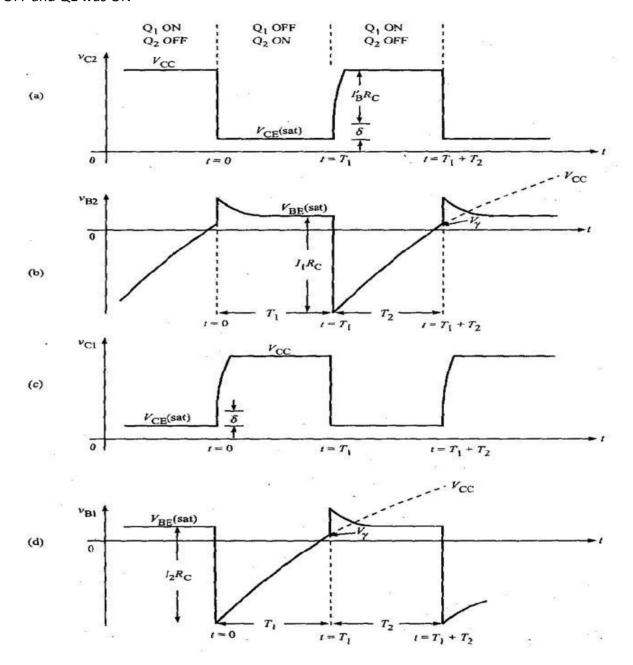

The waveforms at the bases and collectors for the astable multivibrator, are shown in below Figure. Let us say at t=0, Q2 goes to ON state and Q] to OFF state. So, for t<0, Q2 was OFF and Q1 was ON

Fig: waveforms at the bases and collectors of a collector-coupled astable multivibrator

Hence for t < 0, vB2 is negative, vC2 = Vcc, VB! = VBE(sat) and vcj = VCE(sat). The capacitor C2 charges from Vcc through R2 and vB2 rises exponentially towards V cc. At t = 0, vB2 reaches the cut-in voltage Vy and Q2 conducts. As Q2 conducts, its collector voltage Vc2 drops by /2/?c - ^cc ~ VcE( sa O- This drop in vc2 is transmitted to the base of Qj through the coupling capacitor C2

and hence vB1 also falls by /2/?c- Qi goes to OFF state. So, VB] = VBE(sat) - /2tfc, and its collector voltage vcl rises towards VCc- This rise in vc] is coupled through the coupling capacitor C2 to the base of Q2, causing an overshoot § in vB2 and the abrupt rise by the same amount 8 in VCL as shown in Figure 4.51(c). Now since Q2 is ON,  $C\$  charges from Vcc through Rlt and hence VB] rises exponentially. At t = 7"], when VB! rises to VY, Qi conducts and due to regenerative action Qi goes into saturation and Q2 to cut-off. Now, for  $t > T\$ , the coupling capacitor C2 charges from Vcc through R2 and at /= 7", + 7"2, when vB2 rises to the cut-in voltage Vr, Q2 conducts and due to regenerative feedback Q2 goes to ON state and Q| to OFF state. The cycle of events repeats and the circuit keeps on oscillating between its two quasi-stable states. Hence the output is a square wave. It is called a square wave generator or square wave oscillator or relaxation oscillator. It is a free running oscillator.

## Expression for the frequency of oscillation of an astable multivibrator

Consider the waveform at the base of  $Q_1$  shown in Figure 4.54(d). At t = 0,

$$v_{B1} = V_{BE}(sat) - I_2 R_C$$

But

$$I_2 R_C = V_{CC} - V_{CE}(sat)$$

$$\therefore At t = 0, v_{B1} = V_{BE}(sat) - V_{CC} + V_{CE}(sat)$$

For  $0 < t < T_1$ ,  $v_{B1}$  rises exponentially towards  $V_{CC}$  given by the equation,

$$v_o = v_f - (v_f - v_i)e^{-t/\tau}$$

$$\therefore v_{B1} = V_{CC} - [V_{CC} - (V_{BE}(\text{sat}) - V_{CC} + V_{CE}(\text{sat}))]e^{-t/\tau_1}, \text{ where } \tau_1 = R_1C_1$$

At  $t = T_1$ , when  $v_{B1}$  rises to  $V_{\gamma}$ ,  $Q_1$  conducts

$$V_{\gamma} = V_{CC} - [2V_{CC} - (V_{BE}(sat) + V_{CE}(sat))]e^{-T_1/R_1C_1}$$

or

$$e^{T_1/R_1C_1} = \frac{2\left[V_{CC} - \frac{V_{BE}(sat) + V_{CE}(sat)}{2}\right]}{V_{CC} - V_{\gamma}}$$

$$T_1 = R_1 C_1 \ln \frac{2 \left[ V_{CC} - \frac{V_{CE}(\text{sat}) + V_{BE}(\text{sat})}{2} \right]}{V_{CC} - V_{\gamma}}$$

$$T_1 = R_1 C_1 \ln 2 + R_1 C_1 \ln \frac{\left[V_{CC} - \frac{V_{CE}(sat) + V_{BE}(sat)}{2}\right]}{V_{CC} - V_{\gamma}}$$

At room temperature for a transistor,

$$V_{\gamma} = \frac{V_{\text{CE}}(\text{sat}) + V_{\text{BE}}(\text{sat})}{2}$$

$$T_{1} = R_{1}C_{1} \ln 2 = 0.693R_{1}C_{1}$$

Page

On similar lines considering the waveform of above Figure , we can show that the time T2 for which Q2 is OFF and Q1 is ON is given by The period of the waveform, The frequency of oscillation, If  $R\{=R2=R,$  and Cs=C2=C, then TI=T2=T.

$$T = 2 \times 0.693RC = 1.386RC$$

and  $f = \frac{1}{1.386RC}$

The frequency of oscillation may be varied over the range from cycles to mega cycles by varying RC. It is also possible to vary the frequency electrically by connecting R1 and R2 to an auxiliary voltage source V (the collector supply remains +VCC) and then varying this voltage V.

#### THE EMITTER-COUPLED ASTABLE MULTIVIBRATOR

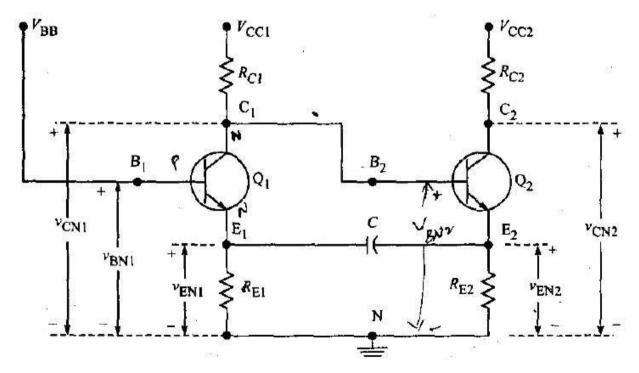

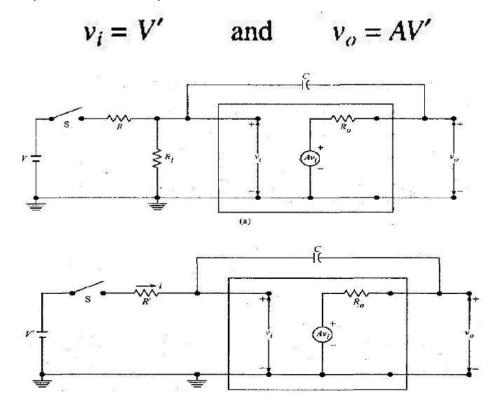

An emitter-coupled astable multivibrator may be obtained by using three power supplies or a single power supply. The below Figure (a) shows the circuit diagram of a free-running emitter coupled multivibrator using n-p-n transistors. Figure 4.64 shows its waveforms. Three power supplies are indicated for the sake of simplifying the analysis. A more practical circuit using a single supply is indicated in below Figure (b). Let us assume that the circuit operates in such a manner that Q1 switches between cut-off and saturation and Q2 switches between cut-off and its active region.

Fig a) Astable Emitter-Coupled Multivibrator

Fig b) Emitter Coupled multivibrator

The waveforms at the base and collector are as shown below:

Fig waveforms of the emitter-coupled astable multivibrator

## **Advantages**

- 1. It is inherently self-starting.

- 2. The collector of Q2 where the output is taken may be loaded heavily even capacitively.

- 3. The output is free of recovery transients.

- 4. Because it has an isolated input at the base of Q1, synchronization is convenient.

- 5. Frequency adjustment is convenient because only one capacitor is used.

## Disadvantages

- 1. This circuit is more difficult to adjust for proper operating conditions.

- 2. This circuit cannot be operated with *T1* and T2 widely different.

- 3. This circuit uses more components than does the collector-coupled circuit.

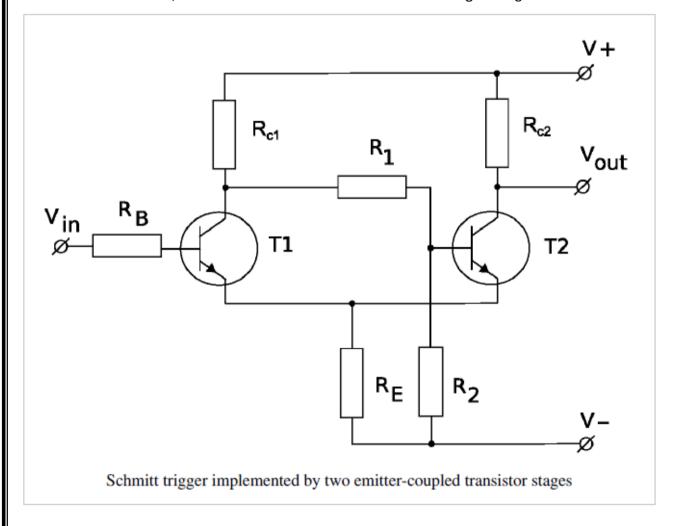

## **Schmitt trigger**

In electronics, **Schmitt trigger** is a circuit with positive feedback and a loop gain >1. The circuit is named "trigger" because the output retains its value until the input changes sufficiently to trigger a change: in the non-inverting configuration, when the input is higher than a certain chosen threshold, the output is high; when the input is below a different (lower) chosen threshold, the output is low; when the input is between the two, the output retains its value. This dual threshold action is called *hysteresis* and implies that the Schmitt trigger possesses memory and can act as a bi-stable circuit (latch). There is a close relation between the two kinds of circuits: a Schmitt trigger can be converted into a latch and a latch can be converted into a Schmitt trigger. Schmitt trigger devices are typically used in open-loop controller configurations for noise immunity and closed loop negative feedback configurations to implement bi-stable regulators, triangle/square wave generators, etc.

The original Schmitt trigger is based on the dynamic threshold idea that is implemented by a voltage divider with a switchable upper leg (the collector resistors Rc1 and Rc2) and a steady lower leg (RE). T1 acts as a comparator with a differential input (T1 base-emitter junction) consisting of an inverting (T1 base) and a non-inverting (T1 emitter) inputs. The input voltage is applied to the inverting input; the output voltage of the voltage divider is applied to the non-inverting input thus determining its threshold. The comparator output drives the second common collector stage T2 (an *emitter follower*) through the voltage follower R1-R2. The emitter-coupled transistors T1 and T2 actually compose an electronic double throw switch that switches over the

upper legs of the voltage divider and changes the threshold in a different (to the input voltage) direction.

This configuration can be considered as a differential amplifier with series positive feedback between its non-inverting input (T2 base) and output (T1 collector) that forces the transition process. There is also a smaller negative feedback introduced by the emitter resistor RE. To make the positive feedback dominate over the negative one and to obtain a hysteresis, the proportion between the two collector resistors is chosen Rc1 > Rc2. Thus less current flows through and less voltage drop is across RE when T1 is switched on than in the case when T2 is switched on. As a result, the circuit has two different thresholds in regard to ground.

## **Operation:**

Initial state. For NPN transistors as shown, imagine the input voltage is below the shared emitter voltage (high threshold for concreteness) so that T1 base-emitter junction is backward-biased and T1 does not conduct. T2 base voltage is determined by the mentioned divider so that T2 is conducting and the trigger output is in the low state. The two resistors Rc2 and RE form

another voltage divider that determines the high threshold. Neglecting VBE, the high threshold value is approximately

$$V_{HT} = \frac{R_E}{R_E + R_{c2}} V_+.$$

The output voltage is low but well above the ground. It is approximately equal to the high threshold and may not be low enough to be a logical zero for next digital circuits. This may require additional shifting circuit following the trigger circuit.

## Crossing up the high threshold:

When the input voltage (T1 base voltage) rises slightly above the voltage across the emitter resistor RE (the high threshold), T1 begins conducting. Its collector voltage goes down and T2 begins going cut-off, because the voltage divider now provides lower T2 base voltage. The common emitter voltage follows this change and goes down thus making T1 conduct more. The current begins steering from the right leg of the circuit to the left one. Although T1 is more conducting, it passes less current through RE (since Rc1 > Rc2); the emitter voltage continues dropping and the effective T1 base-emitter voltage continuously increases. This avalanche-like process continues until T1 becomes completely turned on (saturated) and T2 turned off. The trigger is transitioned to the high state and the output (T2 collector) voltage is close to V+. Now, the two resistors Rc1 and RE form a voltage divider that determines the low threshold. Its value is approximately

$$V_{LT} = \frac{R_E}{R_E + R_{c1}} V_+.$$

### Crossing down the low threshold:

With the trigger now in the high state, if the input voltage lowers enough (below the low threshold), T1 begins cutting-off. Its collector current reduces; as a result, the shared emitter voltage lowers slightly and T1 collector voltage rises significantly. R1-R2 voltage divider conveys this change to T2 base voltage and it begins conducting. The voltage across RE rises, further reducing the T1 base-emitter potential in the same avalanche-like manner, and T1 ceases to conduct. T2 becomes completely turned-on (saturated) and the output voltage becomes low again.

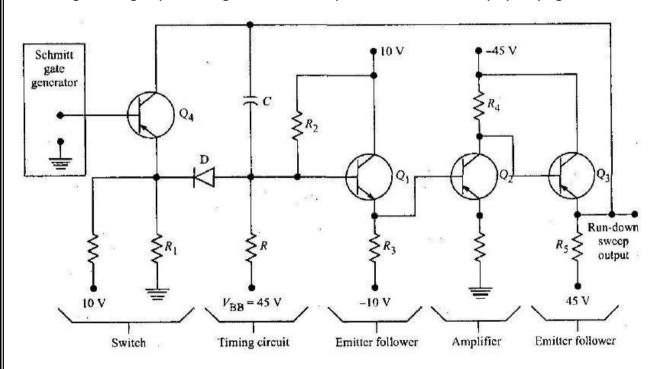

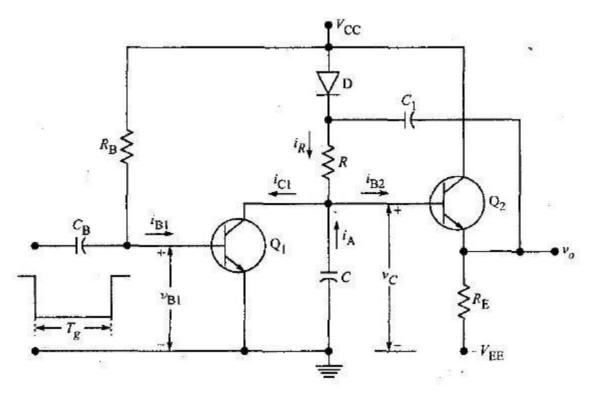

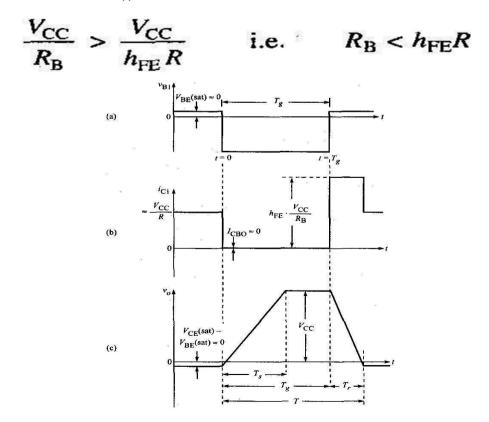

## UNIT –IV TIME BASE GENARATORS

#### TIME BASE GENERATORS

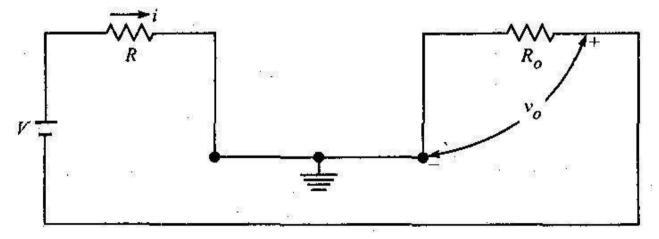

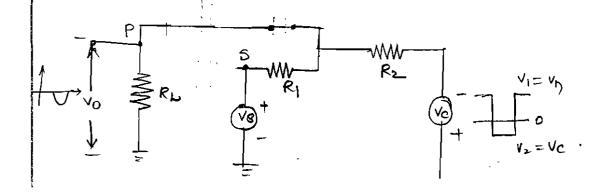

A time-base generator is an electronic circuit which generates an output voltage or current waveform, a portion of which varies linearly with time. Ideally the output waveform should be a ramp. Time-base generators may be voltage time-base generators or current time-base generators. A voltage time-base generator is one that provides an output voltage waveform, a portion of which exhibits a linear variation with respect to time. A current time-base generator is one that provides an output current waveform, a portion of which exhibits a linear variation with respect to time. There are many important applications of time-base generators, such as in CROs, television and radar displays, in precise time measurements, and in time modulation. The most important application of a time-base generator is in CROs. To display the variation with respect to time of an arbitrary waveform on the screen of an oscilloscope it is required to apply to one set of deflecting plates a voltage which varies linearly with time. Since this waveform is used to sweep the electron beam horizontally across the screen it is called the *sweep voltage* and the time-base generators are called the *sweep* circuits.

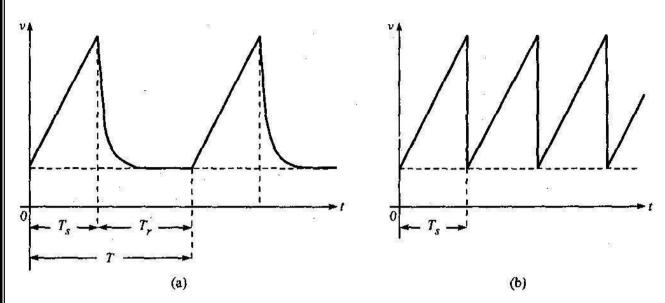

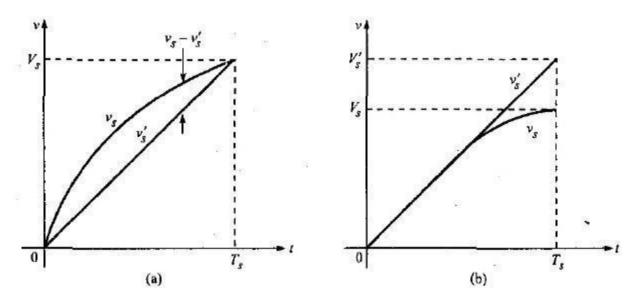

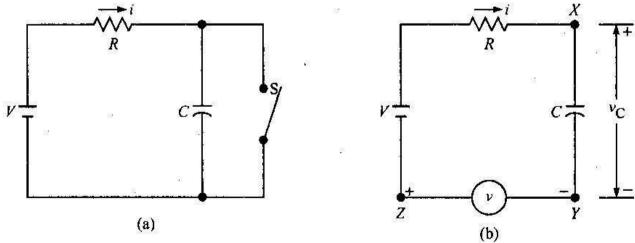

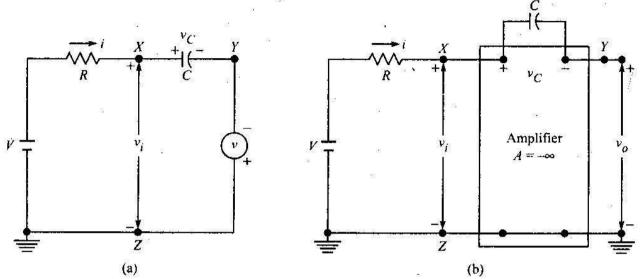

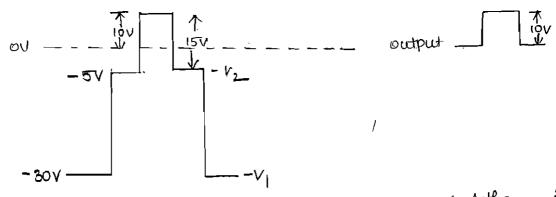

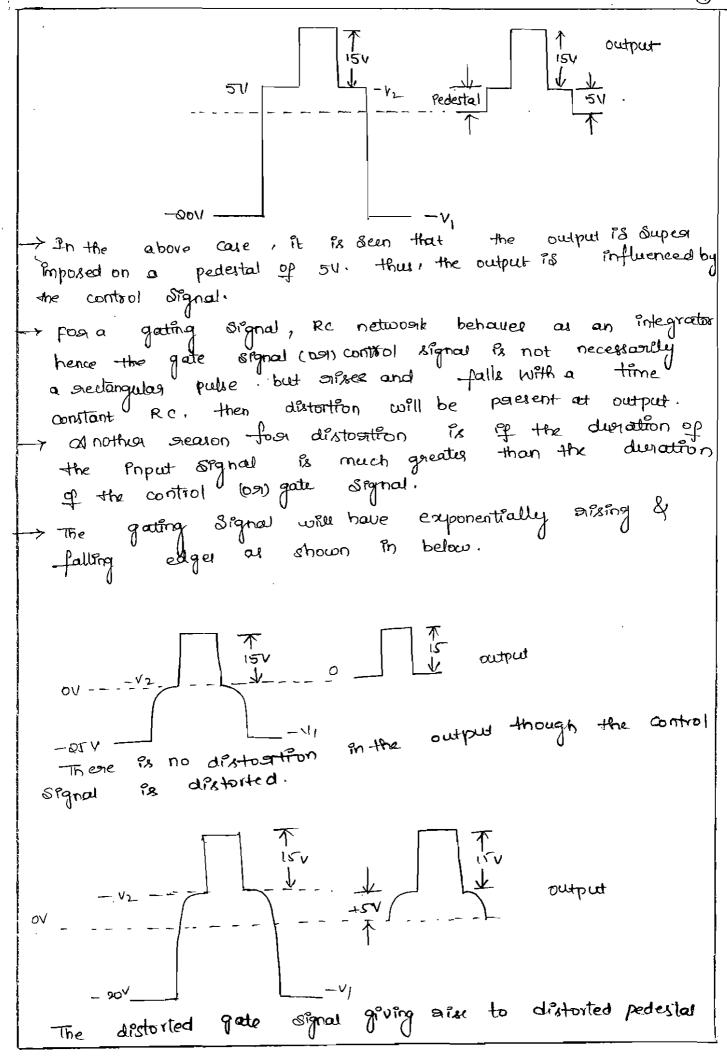

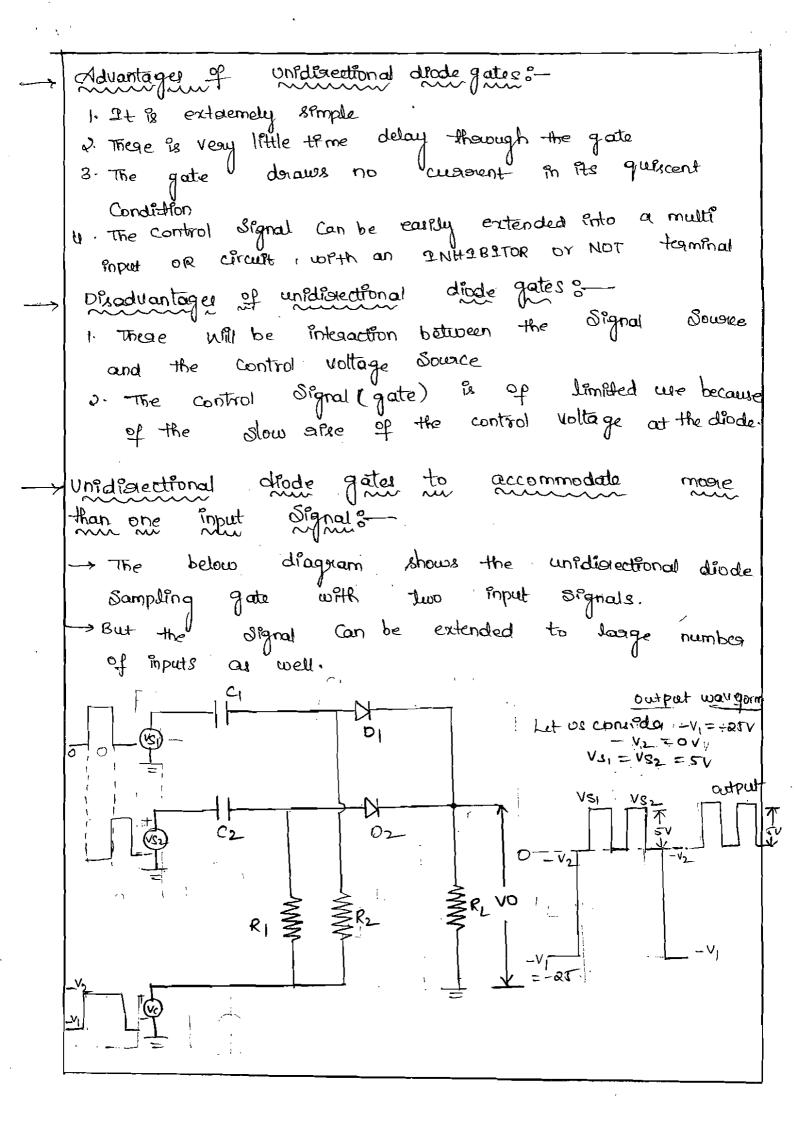

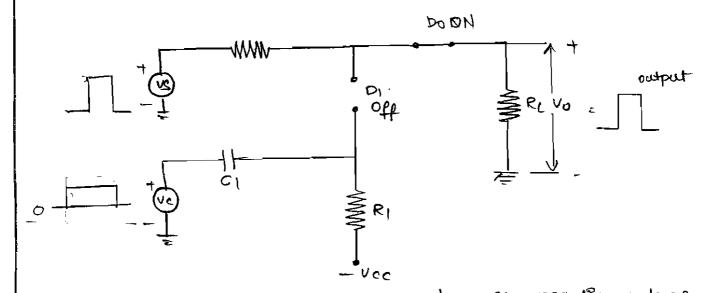

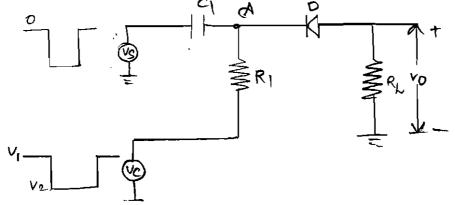

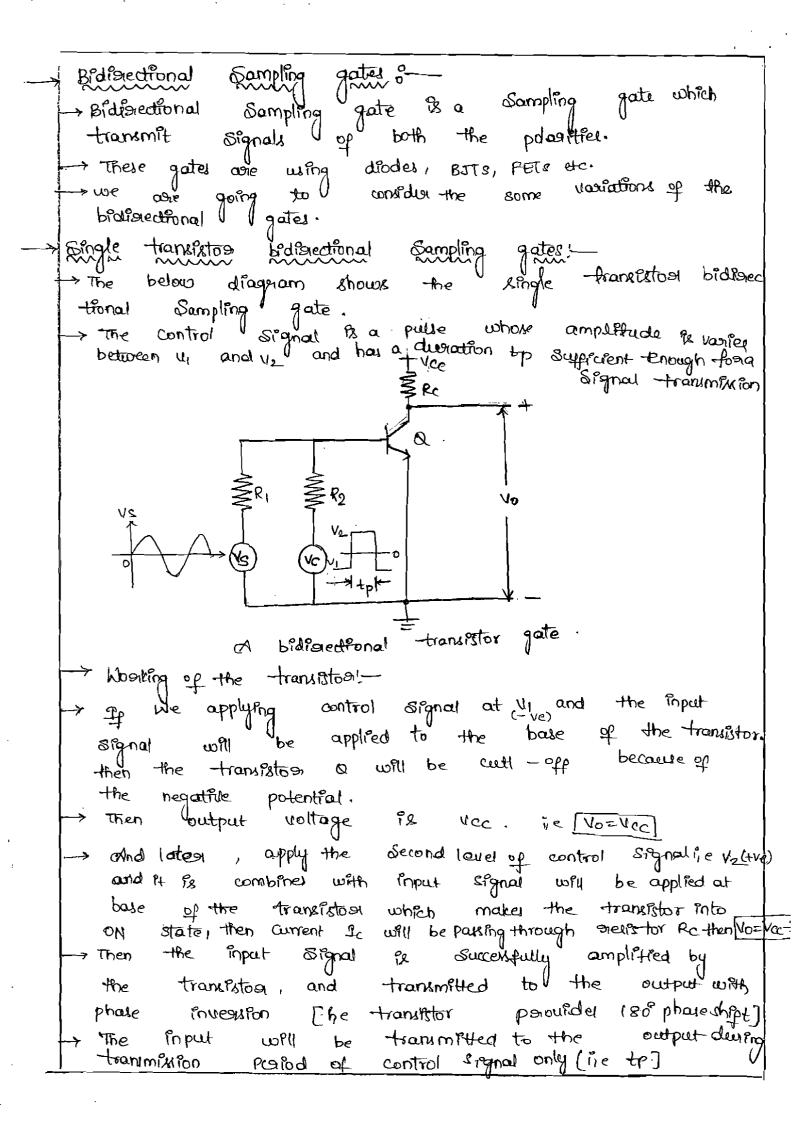

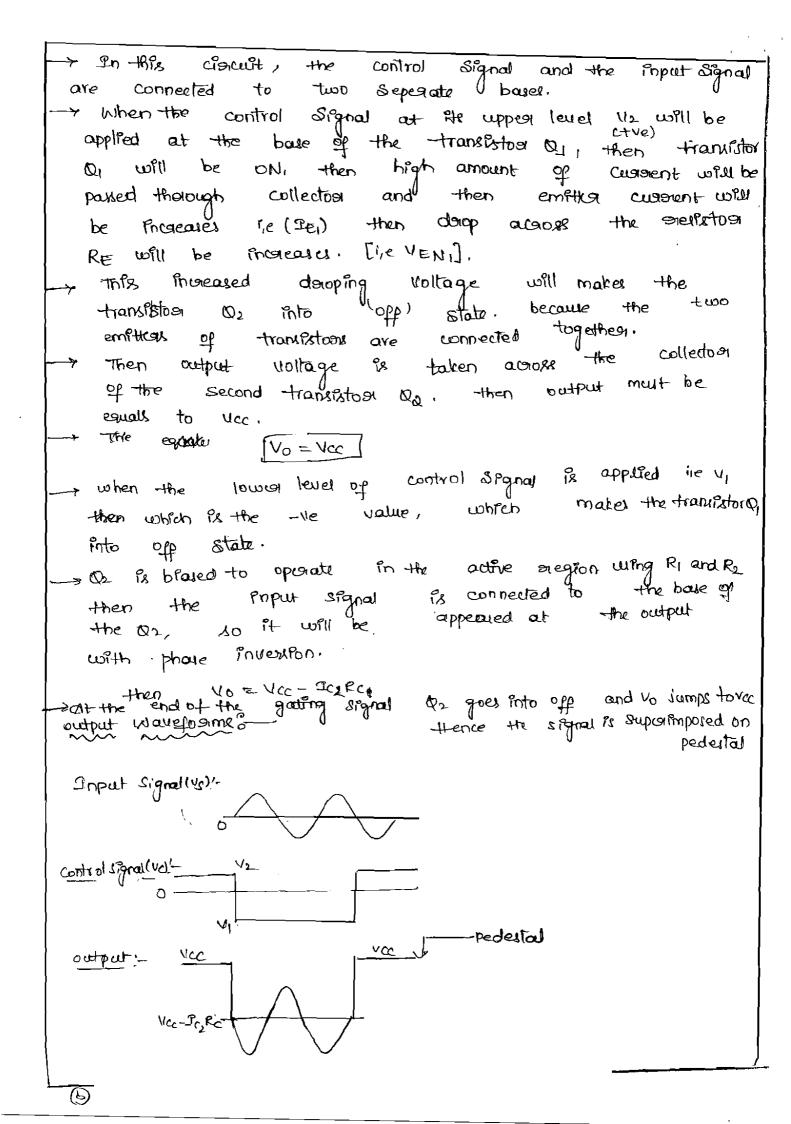

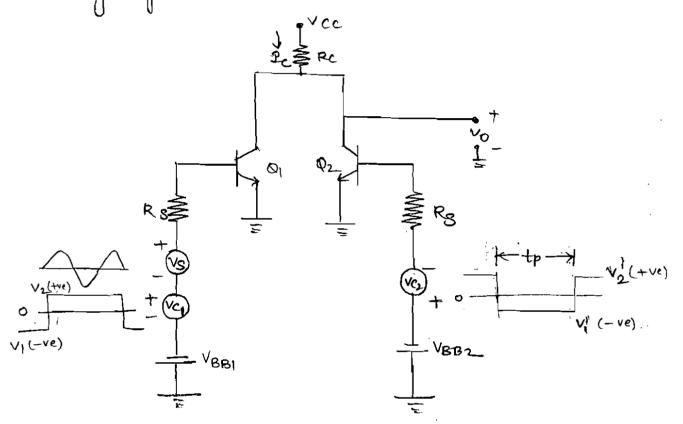

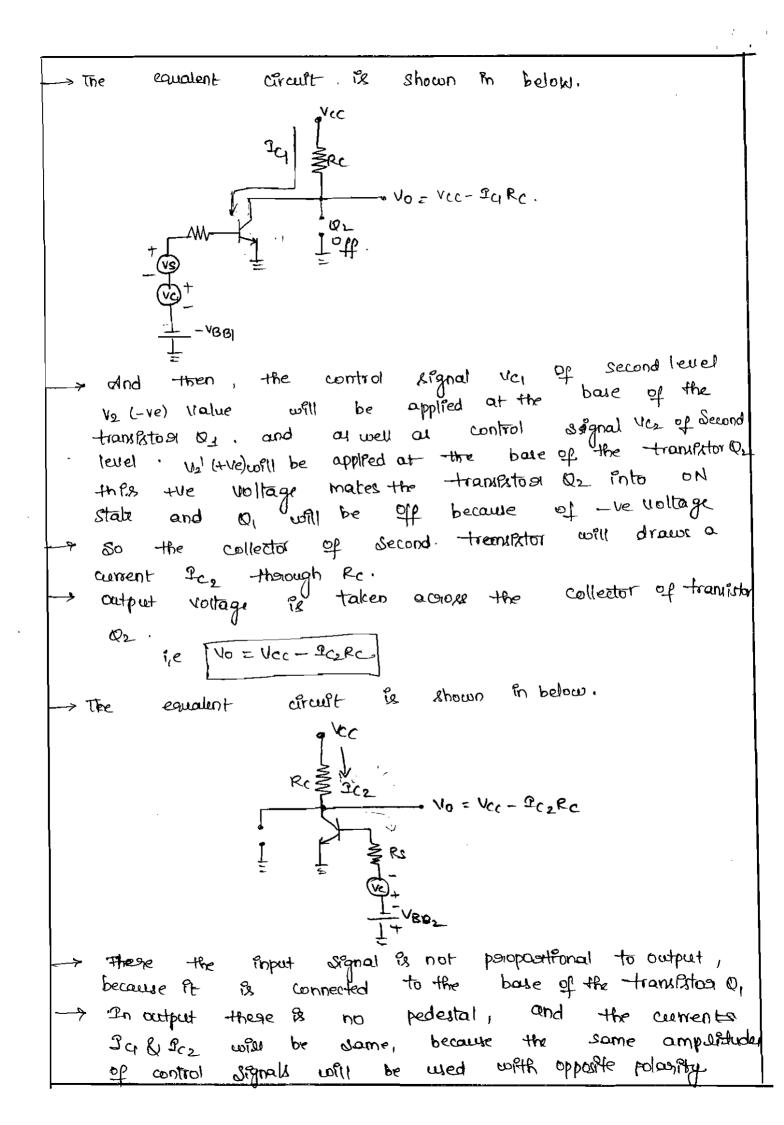

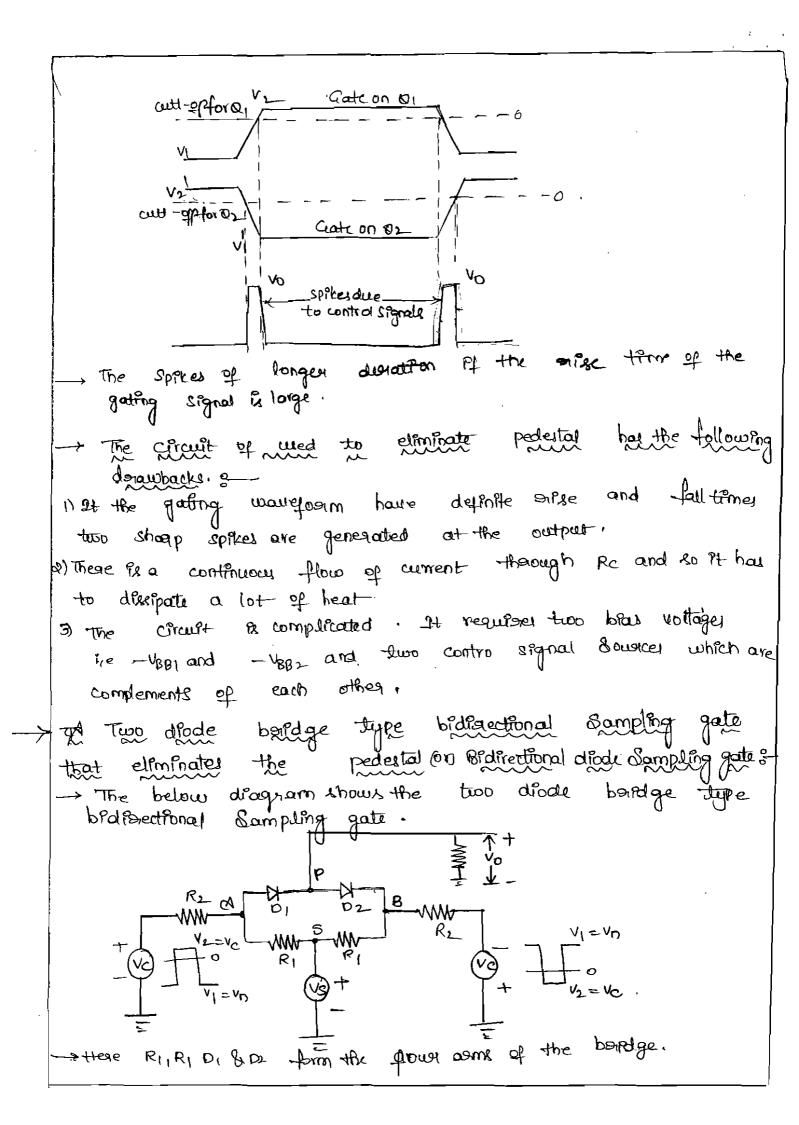

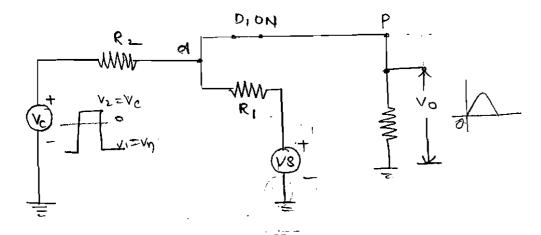

#### **GENERAL FEATURES OF A TIME-BASE SIGNAL**